# FC5A SERIES Micro Programmable Logic Controller

# User's Manual Supplement System Program Version 101 to 210

**IDEC CORPORATION**

# **SAFETY PRECAUTIONS**

- Read this user's manual to make sure of correct operation before starting installation, wiring, operation, maintenance, and inspection of the MicroSmart.

- All MicroSmart modules are manufactured under IDEC's rigorous quality control system, but users must add a backup or failsafe provision to the control system using the MicroSmart in applications where heavy damage or personal injury may be caused in case the MicroSmart should fail.

- In this user's manual, safety precautions are categorized in order of importance to Warning and Caution:

Warning notices are used to emphasize that improper operation may cause severe personal injury or death.

- Turn off the power to the MicroSmart before starting installation, removal, wiring, maintenance, and inspection of the MicroSmart. Failure to turn power off may cause electrical shocks or fire hazard.

- Special expertise is required to install, wire, program, and operate the MicroSmart. People without such expertise must not use the MicroSmart.

- Emergency stop and interlocking circuits must be configured outside the MicroSmart. If such a circuit is configured inside the MicroSmart, failure of the MicroSmart may cause disorder of the control system, damage, or accidents.

- Install the MicroSmart according to the instructions described in this user's manual. Improper installation will result in falling, failure, or malfunction of the MicroSmart.

Caution notices are used where inattention might cause personal injury or damage to equipment.

- The MicroSmart is designed for installation in a cabinet. Do not install the MicroSmart outside a cabinet.

- Install the MicroSmart in environments described in this user's manual. If the MicroSmart is used in places where the MicroSmart is subjected to high-temperature, high-humidity, condensation, corrosive gases, excessive vibrations, and excessive shocks, then electrical shocks, fire hazard, or malfunction will result.

- The environment for using the MicroSmart is "Pollution degree 2." Use the MicroSmart in environments of pollution degree 2 (according to IEC 60664-1).

- Prevent the MicroSmart from falling while moving or transporting the MicroSmart, otherwise damage or malfunction of the MicroSmart will result.

- Prevent metal fragments and pieces of wire from dropping inside the MicroSmart housing. Put a cover on the MicroSmart modules during installation and wiring. Ingress of such fragments and chips may cause fire hazard, damage, or malfunction.

- Use a power supply of the rated value. Use of a wrong power supply may cause fire hazard.

- Use an IEC 60127-approved fuse on the power line outside the MicroSmart. This is required when equipment containing the MicroSmart is destined for Europe.

- Use an IEC 60127-approved fuse on the output circuit. This is required when equipment containing the MicroSmart is destined for Europe.

- Use an EU-approved circuit breaker. This is required when equipment containing the MicroSmart is destined for Europe.

- Make sure of safety before starting and stopping the MicroSmart or when operating the MicroSmart to force outputs on or off. Incorrect operation on the MicroSmart may cause machine damage or accidents.

- If relays or transistors in the MicroSmart output modules should fail, outputs may remain on or off. For output signals which may cause heavy accidents, provide a monitor circuit outside the MicroSmart.

- Do not connect the ground wire directly to the MicroSmart. Connect a protective ground to the cabinet containing the MicroSmart using an M4 or larger screw. This is required when equipment containing the MicroSmart is destined for Europe.

- Do not disassemble, repair, or modify the MicroSmart modules.

- Dispose of the battery in the MicroSmart modules when the battery is dead in accordance with pertaining regulations. When storing or disposing of the battery, use a proper container prepared for this purpose. This is required when equipment containing the MicroSmart is destined for Europe.

- When disposing of the MicroSmart, do so as an industrial waste.

#### **About This Manual**

This user's manual supplement primarily describes in detail the upgraded and new functions added since FC5A Micro-Smart system program version 101 up to 210.

#### CHAPTER 1: UPGRADED FUNCTIONALITY

The list of upgraded and new functions.

#### CHAPTER 2: MODULE SPECIFICATIONS

Updated specifications of analog I/O modules.

#### **CHAPTER 5: SPECIAL FUNCTIONS**

Upgraded functions including HMI module, expansion RS232C communication module, Modbus, 32-bit data storage setting, forced I/O, Run LED flashing mode, memory cartridge upload, user program protection upgrade, and key matrix input.

#### **CHAPTER 7: BASIC INSTRUCTIONS**

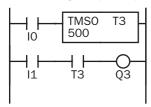

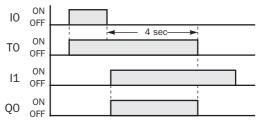

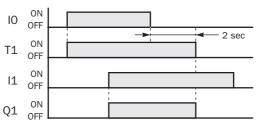

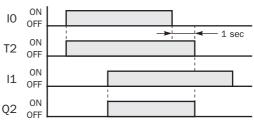

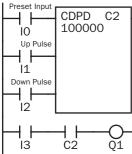

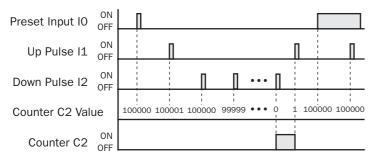

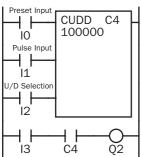

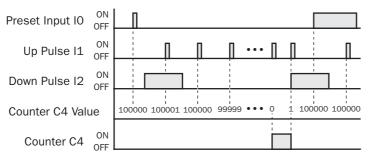

Programming and sample programs of new basic instructions TMLO, TIMO, TMHO, TMSO, CNTD, CDPD, and CUDD.

#### CHAPTERS 8 TO 18 AND CHAPTERS 33 TO 34: ADVANCED INSTRUCTIONS

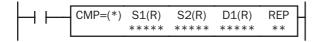

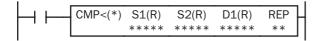

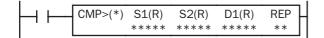

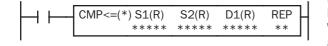

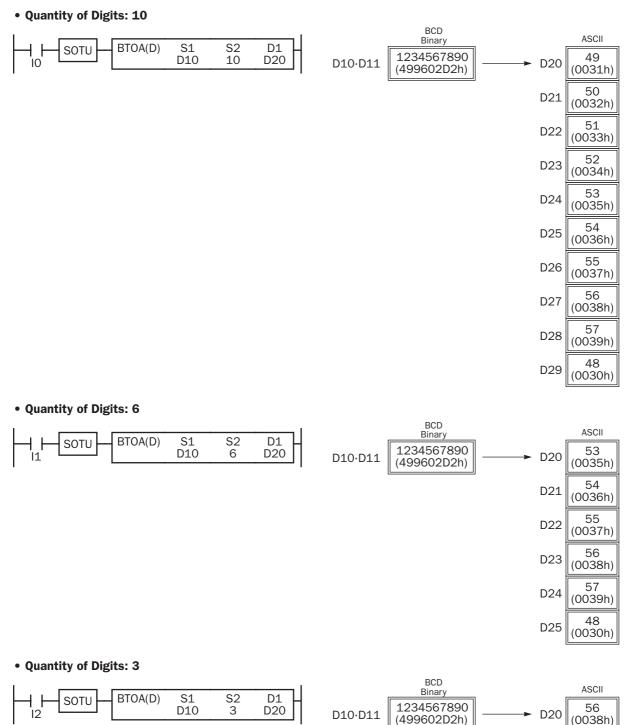

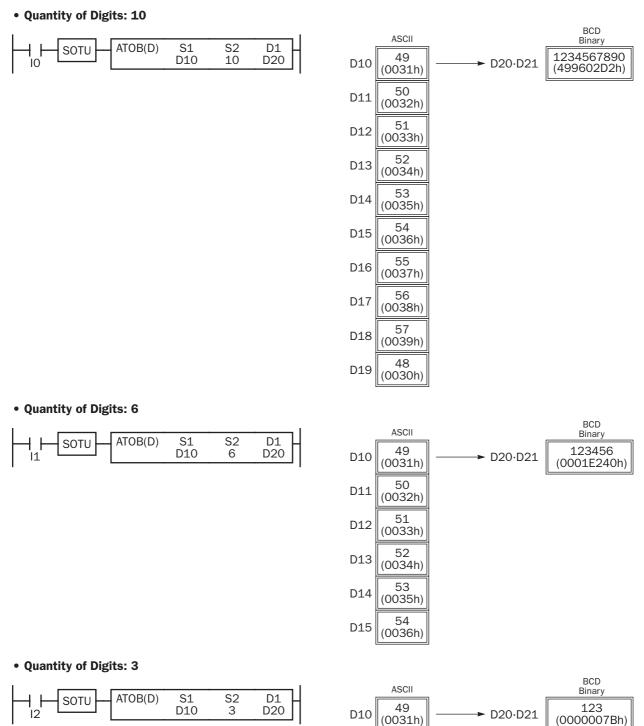

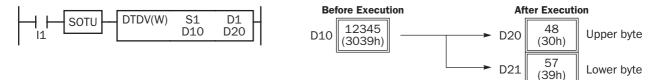

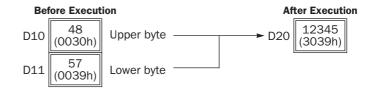

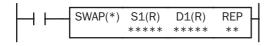

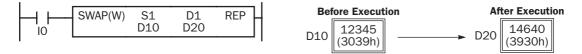

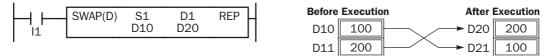

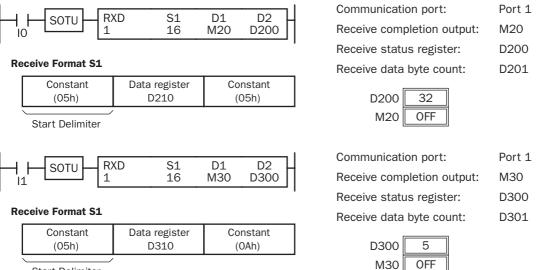

Programming and sample programs of upgraded advanced instructions MOV, IMOV, CMP, ADD, SUB, MUL, DIV, ROOT, BTOA, ATOB, and RXD instructions. Also included are new advanced instructions NSET, NRS, XCHG, TCCST, LC, INC, DEC, SUM, RNDM, DTDV, DTCB, SWAP, DJNZ, FIFOF, FIEX, FOEX, NDSRC, TADD, TSUB, HTOS, STOH, and HOUR.

#### CHAPTER 32: TROUBLESHOOTING

Additional user program execution error codes related to the new advanced instructions.

#### **APPENDIX**

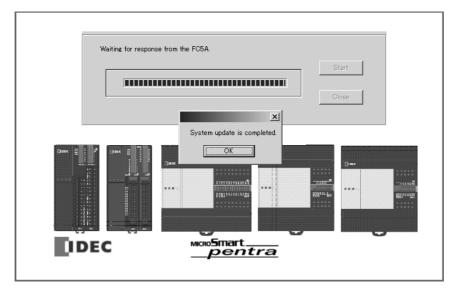

Additional information about execution times for instructions, instruction steps and applicability in interrupt programs, and procedure to upgrade FC5A MicroSmart system program. Also included are corrections in the FC5A MicroSmart User's Manual FC9Y-B927-0.

#### INDEX

Alphabetical listing of key words.

### **IMPORTANT INFORMATION**

Under no circumstances shall IDEC Corporation be held liable or responsible for indirect or consequential damages resulting from the use of or the application of IDEC PLC components, individually or in combination with other equipment.

All persons using these components must be willing to accept responsibility for choosing the correct component to suit their application and for choosing an application appropriate for the component, individually or in combination with other equipment.

All diagrams and examples in this manual are for illustrative purposes only. In no way does including these diagrams and examples in this manual constitute a guarantee as to their suitability for any specific application. To test and approve all programs, prior to installation, is the responsibility of the end user.

# TABLE OF CONTENTS

| CHAPTER 1:                 | UPGRADED FUNCTIONALITY                                                                                                                                                                                                            |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | Upgraded and New Functions List 1-1                                                                                                                                                                                               |

| <b>C</b> HAPTER 2:         | Module Specifications                                                                                                                                                                                                             |

|                            | Analog I/O Module Specifications 2-1                                                                                                                                                                                              |

| <b>C</b> hapter 5:         | Special Functions                                                                                                                                                                                                                 |

|                            | HMI Module5-1Expansion RS232C Communication Module5-2Modbus Communication5-332-bit Data Storage Setting5-4Forced I/O5-7RUN LED Flashing Mode5-9Memory Cartridge Upload5-10User Program Protection Upgrade5-11Key Matrix Input5-12 |

|                            |                                                                                                                                                                                                                                   |

| <u> Снартег 7:</u>         | BASIC INSTRUCTIONS                                                                                                                                                                                                                |

|                            | Basic Instruction List7-1TMLO, TIMO, TMHO, and TMSO (Off-Delay Timer)7-2CNTD, CDPD, and CUDD (Double-Word Counter)7-3                                                                                                             |

| <b>C</b> HAPTER 8:         | Advanced Instructions                                                                                                                                                                                                             |

|                            | Advanced Instruction List       8-1         Advanced Instruction Applicable CPU Modules       8-3                                                                                                                                 |

| <b>C</b> HAPTER 9:         | Move Instructions                                                                                                                                                                                                                 |

|                            | MOV (Move)9-1IMOV (Indirect Move)9-2NSET (N Data Set)9-3NRS (N Data Repeat Set)9-4XCHG (Exchange)9-5TCCST (Timer/Counter Current Value Store)9-6                                                                                  |

| <b>C</b> <u>HAPTER 10:</u> | DATA COMPARISON INSTRUCTIONS                                                                                                                                                                                                      |

|                            | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                             |

| <b>C</b> HAPTER <b>11</b> : | BINARY ARITHMETIC INSTRUCTIONS                                                                                                                                                                           |                       |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|                             | INC (Increment)                                                                                                                                                                                          | 11-1<br>11-3          |

| <u> Снартег 14:</u>         | DATA CONVERSION INSTRUCTIONSBTOA (BCD to ASCII)ATOB (ASCII to BCD)DTDV (Data Divide)DTCB (Data Combine)SWAP (Data Swap)                                                                                  | 14-3<br>14-5<br>14-6  |

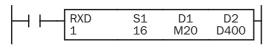

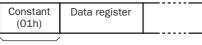

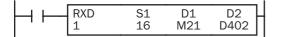

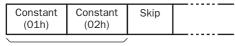

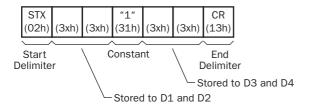

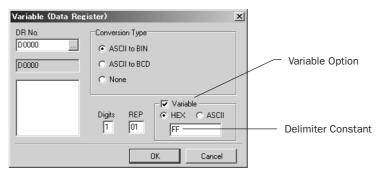

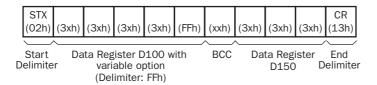

| <u> Снартег 17:</u>         | USER COMMUNICATION INSTRUCTIONS Multi-byte Start Delimiter Constant Variable Option for Data Register User Communication Error                                                                           | 17-4<br>17-5          |

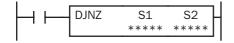

| <b>C</b> <u>HAPTER</u> 18:  | <b>Program Branching Instructions</b> DJNZ (Decrement Jump Non-zero)                                                                                                                                     | 18-1                  |

| <b>С</b> <u>нартег 32:</u>  | <b>TROUBLESHOOTING</b> User Program Execution Error                                                                                                                                                      | 32-1                  |

| <u> Снартег 33:</u>         | FILE DATA PROCESSING INSTRUCTIONS         FIFOF (FIFO Format)         FIEX (First-In Execute)         FOEX (First-Out Execute)         NDSRC (N Data Search)                                             | 33-3<br>33-3          |

| <u>Снартег 34:</u>          | CLOCK INSTRUCTIONS         TADD (Time Addition)         TSUB (Time Subtraction)         HTOS (HMS to Sec)         STOH (Sec to HMS)         HOUR (Hour Meter)                                            | 34-5<br>34-9<br>34-10 |

| <b>A</b> <u>PPENDIX</u>     | Execution Times for InstructionsInstruction Steps and Applicability in Interrupt ProgramsProcedure to Upgrade FC5A MicroSmart System ProgramCorrections in the FC5A MicroSmart User's Manual FC9Y-B927-0 | . A-2<br>. A-3        |

# <u>NDEX</u>

# **1: UPGRADED FUNCTIONALITY**

# **Upgraded and New Functions List**

Upgraded and new functions listed below have been implemented in the FC5A MicroSmart CPU modules. The availability of these functions depends on the model and the system program version of the FC5A MicroSmart CPU modules:

|                                                                       | All-In-O                                               | ne Type                   | Slim Type                                              |               |

|-----------------------------------------------------------------------|--------------------------------------------------------|---------------------------|--------------------------------------------------------|---------------|

| CPU Module                                                            | FC5A-C10R2<br>FC5A-C10R2C<br>FC5A-C16R2<br>FC5A-C16R2C | FC5A-C24R2<br>FC5A-C24R2C | FC5A-D16RK1<br>FC5A-D16RS1<br>FC5A-D32K3<br>FC5A-D32S3 | WindLDR       |

| HMI Module Upgrade (Note 1)                                           | 110 or higher                                          |                           | 101 or higher                                          |               |

| Expansion RS232C Communication Module<br>Compatibility                | _                                                      | 110 or higher             |                                                        |               |

| Modbus Master Upgrade (Note 2)                                        |                                                        |                           | 110 or higher                                          | 5.1 or higher |

| Modbus Slave Upgrade (Note 2)                                         | 110 or highor                                          | 110 or higher             |                                                        |               |

| 32-bit Data Storage Setting                                           | 110 or higher                                          | TTO OL HIGHEI             |                                                        |               |

| Forced I/O                                                            |                                                        |                           |                                                        |               |

| RUN LED Flashing Mode                                                 |                                                        |                           |                                                        |               |

| Memory Cartridge Upload Function (Note 3)                             |                                                        |                           |                                                        |               |

| Off-Delay Timer Instructions<br>(TMLO, TIMO, TMHO, and TMSO)          |                                                        |                           |                                                        |               |

| Double-Word Counter Instructions<br>(CNTD, CDPD, and CUDD)            |                                                        |                           |                                                        |               |

| MOV and IMOV Instructions Upgrade<br>(New data type F)                | -                                                      |                           |                                                        |               |

| N Data Set and N Data Repeat Set Instructions<br>(NSET and NRS)       |                                                        |                           |                                                        |               |

| Timer/Counter Current Value Store Instruction (TCCST)                 | 200 or higher                                          | 200 or higher             | 200 or higher                                          | 5.2 or higher |

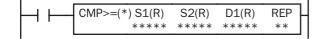

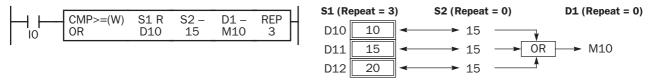

| CMP Instructions Upgrade                                              | -                                                      |                           |                                                        |               |

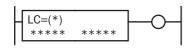

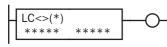

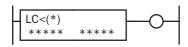

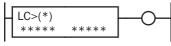

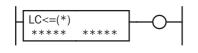

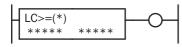

| Load Comparison Instructions<br>(LC=, LC<>, LC<, LC>, LC<=, and LC>=) |                                                        |                           |                                                        |               |

| BTOA and ATOB Instructions Upgrade<br>(New data type D)               |                                                        |                           |                                                        |               |

| Data Divide, Combine, and Swap Instructions<br>(DTDV, DTCB, and SWAP) | 1                                                      |                           |                                                        |               |

| User Communication Instructions Upgrade (RXD)                         |                                                        |                           |                                                        |               |

| File Processing Instructions<br>(FIFOF, FIEX, and FOEX)               |                                                        |                           |                                                        |               |

#### **1: UPGRADED FUNCTIONALITY**

|                                                          | All-In-O                                               | ne Type                   | Slim Type                                              |               |

|----------------------------------------------------------|--------------------------------------------------------|---------------------------|--------------------------------------------------------|---------------|

| CPU Module                                               | FC5A-C10R2<br>FC5A-C10R2C<br>FC5A-C16R2<br>FC5A-C16R2C | FC5A-C24R2<br>FC5A-C24R2C | FC5A-D16RK1<br>FC5A-D16RS1<br>FC5A-D32K3<br>FC5A-D32S3 | WindLDR       |

| Key Matrix Input                                         | _                                                      |                           |                                                        |               |

| User Program Protection Upgrade                          |                                                        |                           |                                                        |               |

| Exchange Instruction (XCHG)                              |                                                        |                           |                                                        |               |

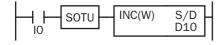

| Increment Instruction (INC)                              |                                                        |                           |                                                        |               |

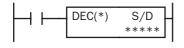

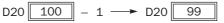

| Decrement Instruction (DEC)                              |                                                        |                           |                                                        |               |

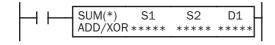

| Sum Instruction (SUM)                                    | 210 or higher                                          | 210 or higher             | 210 or higher                                          | 5.3 or higher |

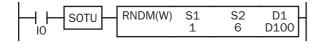

| Random Instruction (RNDM)                                |                                                        |                           |                                                        |               |

| Decrement Jump Non-zero (DJNZ)                           |                                                        |                           |                                                        |               |

| N Data Search Instruction (NDSRC)                        |                                                        |                           |                                                        |               |

| Clock Instructions<br>(TADD, TSUB, HTOS, STOH, and HOUR) |                                                        |                           |                                                        |               |

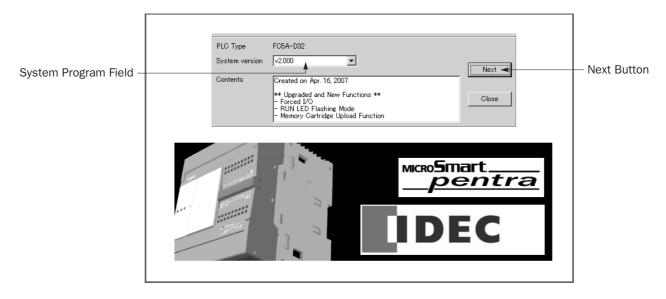

To confirm the system program version of the MicroSmart CPU module, use WindLDR on a computer connected with the CPU module. Bring WindLDR into the online mode. The system program version is indicated on the PLC Status dialog box.

Note 1: The optional HMI module (FC4A-PH1) is needed to use this function.

Note 2: Modbus Master or Slave function can be used on the Port 2 of the MicroSmart CPU modules only.

Note 3: Memory cartridge (FC4A-PM32 or FC4A-PM64) is required to use this function.

#### Introduction

This chapter describes updated analog I/O module specifications.

# Analog I/O Module Specifications

#### **General Specifications (END Refresh Type)**

| Type No.                               | FC4A-L03A1                                                                                                                | FC4A-L03AP1                    | FC4A-J2A1                      | FC4A-K1A1                      |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Rated Power Voltage                    | 24V DC                                                                                                                    |                                |                                |                                |

| Allowable Voltage Range                | 20.4 to 28.8V DC                                                                                                          |                                |                                |                                |

| Terminal Arrangement                   | See Analog I/O Module Terminal Arrangement on pages 2-52 to 2-55 of the FC5A MicroSmart Pentra User's Manual (FC9Y-B927). |                                |                                |                                |

| Connector on Mother Board              | MC1.5/11-G-3.81BK (Phoenix Contact)                                                                                       |                                |                                |                                |

| Connector Insertion/Removal Durability | 100 times minimum                                                                                                         |                                |                                |                                |

| Internal Current Draw                  | 50 mA (5V DC)<br>0 mA (24V DC)                                                                                            | 50 mA (5V DC)<br>0 mA (24V DC) | 50 mA (5V DC)<br>0 mA (24V DC) | 50 mA (5V DC)<br>0 mA (24V DC) |

| External Current Draw (Note)           | 45 mA (24V DC)                                                                                                            | 40 mA (24V DC)                 | 35 mA (24V DC)                 | 40 mA (24V DC)                 |

| Weight                                 | 85g                                                                                                                       | •                              |                                |                                |

Note: The external current draw is the value when all analog inputs are used and the analog output value is at 100%.

#### **General Specifications (Ladder Refresh Type)**

| Type No.                               | FC4A-J4CN1                                                                                                                | FC4A-J8C1                      | FC4A-J8AT1                     | FC4A-K2C1                      |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Rated Power Voltage                    | 24V DC                                                                                                                    |                                |                                |                                |

| Allowable Voltage Range                | 18.0 to 30.0V DC                                                                                                          |                                |                                |                                |

| Terminal Arrangement                   | See Analog I/O Module Terminal Arrangement on pages 2-52 to 2-55 of the FC5A MicroSmart Pentra User's Manual (FC9Y-B927). |                                |                                |                                |

| Connector on Mother Board              | MC1.5/10-G-3.81BK (Phoenix Contact)                                                                                       |                                |                                |                                |

| Connector Insertion/Removal Durability | 100 times minimu                                                                                                          | m                              |                                |                                |

| Internal Current Draw                  | 50 mA (5V DC)<br>0 mA (24V DC)                                                                                            | 40 mA (5V DC)<br>0 mA (24V DC) | 45 mA (5V DC)<br>0 mA (24V DC) | 60 mA (5V DC)<br>0 mA (24V DC) |

| External Current Draw (Note)           | 55 mA (24V DC)                                                                                                            | 50 mA (24V DC)                 | 55 mA (24V DC)                 | 85 mA (24V DC)                 |

| Weight                                 | 140g                                                                                                                      | 140g                           | 125g                           | 110g                           |

Note: The external current draw is the value when all analog inputs are used and the analog output value is at 100%.

#### **2: MODULE SPECIFICATIONS**

#### Analog Input Specifications (END Refresh Type)

| Type No.                            |                                                                 | FC4A-L03A1                                                                                           | / FC4A-J2A1                | FC4A-                                                                                       | L03AP1                                   |  |  |

|-------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------|------------------------------------------|--|--|

| Analog Input                        | Signal Type                                                     | Voltage Input                                                                                        | Current Input              | Thermocouple                                                                                | Resistance<br>Thermometer                |  |  |

| Input Range                         |                                                                 | 0 to 10V DC                                                                                          | 4 to 20 mA DC              | Type K<br>(0 to 1300°C)<br>Type J<br>(0 to 1200°C)<br>Type T<br>(0 to 400°C)                | Pt 100<br>3-wire type<br>(-100 to 500°C) |  |  |

| Input Impeda                        | nce                                                             | $1 M\Omega$ minimum                                                                                  | 10Ω                        | $1 M\Omega$ minimum                                                                         | $1 M\Omega$ minimum                      |  |  |

| Allowable Co<br>(per wire)          | nductor Resistance                                              | _                                                                                                    | _                          | _                                                                                           | $200\Omega$ maximum                      |  |  |

| Input Detecti                       | ion Current                                                     | —                                                                                                    | —                          | —                                                                                           | 1.0 mA maximum                           |  |  |

|                                     | Sample Duration Time                                            | 20 ms maximum                                                                                        | 1                          | 20 ms maximum                                                                               |                                          |  |  |

|                                     | Sample Repetition Time                                          | 20 ms maximum                                                                                        |                            | 20 ms maximum                                                                               |                                          |  |  |

| AD                                  | Total Input System<br>Transfer Time (Note 1)                    | 105 ms + 1 scar                                                                                      | n time                     | 200 ms + 1 scan                                                                             | time                                     |  |  |

| Conversion                          | Type of Input                                                   | Single-ended input                                                                                   |                            |                                                                                             |                                          |  |  |

| Operating Mode                      |                                                                 | Self-scan                                                                                            |                            |                                                                                             |                                          |  |  |

|                                     | Conversion Method                                               | $\sum \Delta$ type ADC                                                                               |                            |                                                                                             |                                          |  |  |

| Input Error                         | Maximum Error at 25°C                                           | ±0.2% of full scale                                                                                  |                            | ±0.2% of full scale<br>+ reference<br>junction compen-<br>sation accuracy<br>(±4°C maximum) | ±0.2% of full scale                      |  |  |

|                                     | Temperature Coefficient                                         | ±0.006% of full s                                                                                    |                            |                                                                                             |                                          |  |  |

|                                     | Repeatability after<br>Stabilization Time                       | ±0.5% of full scale                                                                                  |                            |                                                                                             |                                          |  |  |

|                                     | Non-lineality                                                   | ±0.2% of full scale                                                                                  |                            |                                                                                             |                                          |  |  |

|                                     | Maximum Error                                                   | ±1% of full scale                                                                                    |                            |                                                                                             |                                          |  |  |

|                                     | Digital Resolution                                              | 4096 increments                                                                                      | s (12 bits)                |                                                                                             |                                          |  |  |

| Data                                | Input Value of LSB                                              | 2.5 mV                                                                                               | 4 μΑ                       | K: 0.325°C<br>J: 0.300°C<br>T: 0.100°C                                                      | 0.15°C                                   |  |  |

| Data                                | Data Type in Application<br>Program                             | Default: 0 to 4095<br>Optional: –32768 to 32767 (selectable each channel) (Note 2)                   |                            |                                                                                             |                                          |  |  |

|                                     | Monotonicity                                                    | Yes                                                                                                  |                            |                                                                                             |                                          |  |  |

|                                     | Input Data Out of Range                                         | Detectable (Note                                                                                     | 3)                         |                                                                                             |                                          |  |  |

| Nelec                               | Maximum Temporary<br>Deviation during Electrical<br>Noise Tests | ±3% maximum<br>(when a 500V cla<br>supply and I/O lin                                                | amp voltage is app<br>nes) | lied to the power                                                                           | Not assured                              |  |  |

| Noise<br>Resistance                 | Input Filter                                                    | No                                                                                                   |                            |                                                                                             |                                          |  |  |

| Resistance                          | Recommended Cable for<br>Noise Immunity                         | Twisted pair shie                                                                                    | lded cable                 | _                                                                                           |                                          |  |  |

|                                     | Crosstalk                                                       | 2 LSB maximum                                                                                        |                            |                                                                                             |                                          |  |  |

| Isolation                           |                                                                 | Isolated between input and power circuit<br>Photocoupler-isolated between input and internal circuit |                            |                                                                                             |                                          |  |  |

| Effect of Improper Input Connection |                                                                 | No damage                                                                                            |                            |                                                                                             |                                          |  |  |

|                                     | rmanent Allowed Overload                                        | 13V DC 40 mA DC —                                                                                    |                            |                                                                                             |                                          |  |  |

| Selection of /                      | Analog Input Signal Type                                        | Using software p                                                                                     | rogramming                 |                                                                                             |                                          |  |  |

| Calibration of Rated Accura         | r Verification to Maintain<br>acy                               | Impossible                                                                                           |                            |                                                                                             |                                          |  |  |

For Note 1 through Note 3, see page 2-6.

| Type No.                 |                                              | FC4A-J4CN1                                                         | / FC4A-J8C1                             | FC4A                                                                                | -J4CN1                                                                         |  |  |

|--------------------------|----------------------------------------------|--------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|

| Analog Input Signal Type |                                              | Voltage Input Current Input                                        |                                         | Thermocouple                                                                        | Resistance<br>Thermometer                                                      |  |  |

| Input Range              |                                              | 0 to 10V DC                                                        | 4 to 20 mA DC                           | Type K:<br>0 to 1300°C<br>Type J:<br>0 to 1200°C<br>Type T:<br>0 to 400°C           | Pt100, Pt1000:<br>-100 to 500°C<br>Ni100, Ni1000:<br>-60 to 180°C              |  |  |

| Input Impedance          |                                              | 1 ΜΩ                                                               | FC4A-J4CN1:<br>7Ω<br>FC4A-J8C1:<br>100Ω | - 1 ΜΩ                                                                              |                                                                                |  |  |

| Input Detect             | ion Current                                  | —                                                                  | —                                       | —                                                                                   | 0.1 mA                                                                         |  |  |

| Sample Duration Time     |                                              | 2 ms maximum                                                       |                                         |                                                                                     |                                                                                |  |  |

| AD<br>Conversion         | Sample Repetition Time                       |                                                                    | ) ms maximum<br>ms maximum              | 30 ms maximum                                                                       | 10 ms maximum                                                                  |  |  |

|                          | Total Input System<br>Transfer Time (Note 1) | FC4A-J4CN1:<br>50 ms × channels<br>FC4A-J8C1:<br>8 ms × channels - |                                         | 85 ms<br>× channels<br>+ 1 scan time                                                | 50 ms<br>× channels<br>+ 1 scan time                                           |  |  |

|                          | Type of Input                                | Single-ended input                                                 |                                         |                                                                                     |                                                                                |  |  |

|                          | Operating Mode                               | Self-scan                                                          |                                         |                                                                                     |                                                                                |  |  |

|                          | Conversion Method                            | FC4A-J4CN1: ∑∆ type ADC                                            |                                         | ation register method                                                               | I                                                                              |  |  |

|                          | Maximum Error at 25°C                        | ±0.2% of full scale                                                |                                         | ±0.2% of full scale<br>+ cold junction<br>compensation<br>error (±3°C maxi-<br>mum) | Pt100, Ni100:<br>±0.4% of full scale<br>Pt1000, Ni1000:<br>±0.2% of full scale |  |  |

| Input Error              | Cold Junction<br>Compensation Error          | -                                                                  | _                                       | ±3.0°C<br>maximum                                                                   | —                                                                              |  |  |

|                          | Temperature Coefficient                      | ±0.005% of full so                                                 | ±0.005% of full scale/°C                |                                                                                     |                                                                                |  |  |

|                          | Repeatability after<br>Stabilization Time    | ±0.5% of full scale                                                | 9                                       |                                                                                     |                                                                                |  |  |

|                          | Non-lineality                                | ±0.04% of full sca                                                 | ale                                     |                                                                                     |                                                                                |  |  |

|                          | Maximum Error                                | ±1% of full scale                                                  |                                         |                                                                                     |                                                                                |  |  |

Analog Input Specifications (Ladder Refresh Type)

## 2: MODULE SPECIFICATIONS

| Type No.                            |                                                                 | FC4A-J4CN1                                                                 | / FC4A-J8C1   | FC4A                                                                                                                                      | -J4CN1                                                                                                                                                                                                   |  |

|-------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Analog Input Signal Type            |                                                                 | Voltage Input                                                              | Current Input | Thermocouple                                                                                                                              | Resistance<br>Thermometer                                                                                                                                                                                |  |

| Digital Resolution                  |                                                                 | 50000 increments                                                           | s (16 bits)   | K: Approx.<br>24000 increments<br>(15 bits)<br>J: Approx.<br>33000 increments<br>(15 bits)<br>T: Approx.<br>10000 increments<br>(14 bits) | Pt100: Approx.<br>6400 increments<br>(13 bits)<br>Pt1000: Approx.<br>64000 increments<br>(16 bits)<br>Ni100: Approx.<br>4700 increments<br>(13 bits)<br>Ni1000: Approx.<br>47000 increments<br>(16 bits) |  |

| Data                                | Input Value of LSB                                              | 0.2 mV                                                                     | 0.32 μΑ       | K: 0.058°C<br>J: 0.038°C<br>T: 0.042°C                                                                                                    | Pt100: 0.086°C<br>Pt1000: 0.0086°C<br>Ni100: 0.037°C<br>Ni1000: 0.0037°C                                                                                                                                 |  |

| -                                   | Data Type in Application<br>Program                             | Default: 0 to 50000                                                        |               | Default:<br>0 to 50000                                                                                                                    | Pt100, Ni100:<br>0 to 6000<br>Pt1000, Ni1000:<br>0 to 60000                                                                                                                                              |  |

|                                     |                                                                 | Optional: -32768 to 32767 (selectable for each channel) (Note 2)           |               |                                                                                                                                           |                                                                                                                                                                                                          |  |

|                                     |                                                                 | — Temperature: Celsius, Fahrenheit                                         |               |                                                                                                                                           |                                                                                                                                                                                                          |  |

|                                     | Monotonicity                                                    | Yes                                                                        |               |                                                                                                                                           |                                                                                                                                                                                                          |  |

|                                     | Input Data Out of Range                                         | Detectable (Note 3                                                         | 3)            |                                                                                                                                           |                                                                                                                                                                                                          |  |

|                                     | Maximum Temporary<br>Deviation during<br>Electrical Noise Tests | ±3% maximum<br>(when a 500V clamp voltage is applied<br>ply and I/O lines) |               | d to the power sup-                                                                                                                       | Not assured                                                                                                                                                                                              |  |

| Noise<br>Resistance                 | Input Filter                                                    | Software                                                                   |               |                                                                                                                                           |                                                                                                                                                                                                          |  |

| Nooiotanoc                          | Recommended Cable for<br>Noise Immunity                         | Twisted pair cable                                                         |               | _                                                                                                                                         |                                                                                                                                                                                                          |  |

|                                     | Crosstalk 2 LSB maximum                                         |                                                                            |               |                                                                                                                                           |                                                                                                                                                                                                          |  |

| Isolation                           |                                                                 | Isolated between input and power circuit                                   |               |                                                                                                                                           |                                                                                                                                                                                                          |  |

| Isolation                           |                                                                 | Photocoupler-isolated between input and internal circuit                   |               |                                                                                                                                           |                                                                                                                                                                                                          |  |

| Effect of Improper Input Connection |                                                                 | No damage                                                                  |               |                                                                                                                                           |                                                                                                                                                                                                          |  |

| (No Damage                          |                                                                 | 11V DC                                                                     | 22 mA DC      |                                                                                                                                           |                                                                                                                                                                                                          |  |

| Selection of                        | Analog Input Signal Type                                        | Using software pro                                                         | ogramming     |                                                                                                                                           |                                                                                                                                                                                                          |  |

| Calibration o<br>Rated Accur        | or Verification to Maintain<br>acy                              | Impossible                                                                 |               |                                                                                                                                           |                                                                                                                                                                                                          |  |

For Note 1 through Note 3, see page 2-6.

### Analog Input Specifications (Ladder Refresh Type)

| Type No.                                |                                                                 | FC4                                                                                                  | A-J8AT1                                         |  |  |

|-----------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|

| Analog Input                            | Signal Type                                                     | NTC                                                                                                  | PTC                                             |  |  |

| Input Range                             |                                                                 | –50 to 150°C                                                                                         | •                                               |  |  |

| Applicable T                            | hermistor                                                       | 100 kΩ maximum                                                                                       |                                                 |  |  |

| Input Detect                            | ion Current                                                     | 0.1 mA                                                                                               |                                                 |  |  |

|                                         | Sample Duration Time                                            | 2 ms maximum                                                                                         |                                                 |  |  |

|                                         | Sample Repetition Time                                          | 2 ms maximum                                                                                         |                                                 |  |  |

| AD<br>Conversion                        | Total Input System<br>Transfer Time (Note 1)                    | 10 ms × channels + 1 scan time (No                                                                   | ote 1)                                          |  |  |

| Conversion                              | Type of Input                                                   | Single-ended input                                                                                   |                                                 |  |  |

|                                         | Operating Mode                                                  | Self-scan                                                                                            |                                                 |  |  |

|                                         | Conversion Method                                               | Successive approximation register m                                                                  | nethod                                          |  |  |

|                                         | Maximum Error at 25°C                                           | ±0.2% of full scale                                                                                  |                                                 |  |  |

|                                         | Temperature Coefficient                                         | ±0.005% of full scale/°C                                                                             |                                                 |  |  |

| Input Error                             | Repeatability after<br>Stabilization Time                       | ±0.5% of full scale                                                                                  |                                                 |  |  |

|                                         | Non-lineality                                                   | No                                                                                                   |                                                 |  |  |

|                                         | Maximum Error                                                   | ±1% of full scale                                                                                    |                                                 |  |  |

|                                         | Digital Resolution                                              | Approx. 4000 increments (12 bits)                                                                    |                                                 |  |  |

| _                                       | Input Value of LSB                                              | 0.05°C                                                                                               |                                                 |  |  |

| Data                                    | Data Type in Application<br>Program                             | Default:0 to 4000Optional:-32768 to 32767 (seTemperature:Celsius, Fahrenheit (NResistance:0 to 10000 | lectable for each channel) (Note 2)<br>TC only) |  |  |

|                                         | Monotonicity                                                    | Yes                                                                                                  |                                                 |  |  |

|                                         | Input Data Out of Range                                         | Detectable (Note 3)                                                                                  |                                                 |  |  |

|                                         | Maximum Temporary<br>Deviation during<br>Electrical Noise Tests | ±3% maximum<br>(when a 500V clamp voltage is appli                                                   | ed to the power supply and I/O lines            |  |  |

| Noise<br>Resistance                     | Input Filter                                                    | Software                                                                                             |                                                 |  |  |

| Recommended Cable for<br>Noise Immunity |                                                                 | _                                                                                                    |                                                 |  |  |

|                                         | Crosstalk                                                       | 2 LSB maximum                                                                                        |                                                 |  |  |

| Isolation                               |                                                                 | Isolated between input and power cir                                                                 | rcuit                                           |  |  |

| 1901011011                              |                                                                 | Photocoupler-isolated between input                                                                  | and internal circuit                            |  |  |

| Effect of Imp                           | proper Input Connection                                         | No damage                                                                                            |                                                 |  |  |

| Selection of                            | Analog Input Signal Type                                        | Using software programming                                                                           |                                                 |  |  |

| Calibration o<br>Rated Accur            | r Verification to Maintain<br>acy                               | Impossible                                                                                           |                                                 |  |  |

For Note 1 through Note 3, see page 2-6.

#### **Analog Output Specifications**

| Category                                                                                            |                                                                 |           |                                                                                            | END Refresh Type                                       |                              | Ladder Refresh                   |  |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------|----------------------------------|--|

| Туре No.                                                                                            |                                                                 |           | FC4A-L03A1                                                                                 | FC4A-L03AP1                                            | FC4A-K1A1                    | FC4A-K2C1                        |  |

| Autout Denge                                                                                        |                                                                 | Voltage   | 0 to 10V DC                                                                                |                                                        |                              | -10 to +10V DC                   |  |

| Output Range                                                                                        |                                                                 | Current   | 4 to 20 mA DC                                                                              |                                                        |                              |                                  |  |

| Load                                                                                                | Load Impedan                                                    | ce        | 2 kΩ minimum (voltage), 300Ω maximum (current)                                             |                                                        |                              |                                  |  |

| Load                                                                                                | Applicable Loa                                                  | ad Type   | Resistive load                                                                             |                                                        |                              |                                  |  |

| DA                                                                                                  | Settling Time                                                   |           | 50 ms                                                                                      | 130 ms                                                 | 50 ms                        | 1 ms/ch                          |  |

| DA<br>Conversion                                                                                    | Total Output S<br>Transfer Time                                 | System    | Settling time + 1                                                                          | scan time                                              |                              | 1 ms × channels<br>+ 1 scan time |  |

|                                                                                                     | Maximum Erro<br>25°C                                            | or at     | ±0.2% of full sca                                                                          | le                                                     |                              |                                  |  |

|                                                                                                     | Temperature<br>Coefficient                                      |           | ±0.015% of full s                                                                          | scale/°C                                               |                              | ±0.005% of full<br>scale/°C      |  |

| Output Error                                                                                        | Repeatability a Stabilization T                                 | ime       | ±0.5% of full sca                                                                          | le                                                     |                              |                                  |  |

|                                                                                                     | Output Voltage Drop                                             |           | ±1% of full scale                                                                          |                                                        |                              |                                  |  |

| Non-lineality                                                                                       |                                                                 |           | ±0.2% of full sca                                                                          |                                                        |                              |                                  |  |

| Output Ripple                                                                                       |                                                                 |           | 1 LSB maximum                                                                              |                                                        |                              | ±0.1% of full scale              |  |

|                                                                                                     | Overshoot                                                       |           | 0%                                                                                         |                                                        |                              |                                  |  |

|                                                                                                     | <b>Total Error</b>                                              |           | ±1% of full scale                                                                          |                                                        |                              |                                  |  |

|                                                                                                     | Digital Resolution                                              |           | 4096 increments (12 bits)                                                                  |                                                        |                              | 50000 increments<br>(16 bits)    |  |

|                                                                                                     | <b>Output Value</b>                                             | Voltage   | 2.5 mV                                                                                     |                                                        |                              | 0.4 mV                           |  |

|                                                                                                     | of LSB Current                                                  |           | 4 μΑ                                                                                       |                                                        | 0.32 µA                      |                                  |  |

| Data                                                                                                | Data Type in                                                    | 1         | Default: 0 to 4095 (voltage, current)                                                      |                                                        | -25000 to 25000<br>(voltage) |                                  |  |

|                                                                                                     | Application Program                                             |           |                                                                                            |                                                        |                              | 0 to 50000<br>(current)          |  |

|                                                                                                     |                                                                 |           | Optional: -32768 to 32767 (selectable for each channel) (Note 2)                           |                                                        |                              |                                  |  |

|                                                                                                     | Monotonicity                                                    |           | Yes                                                                                        |                                                        |                              |                                  |  |

| Current Loop O                                                                                      | -                                                               |           | Not detectable                                                                             |                                                        |                              |                                  |  |

| Noise                                                                                               | Maximum Temporary<br>Deviation during<br>Electrical Noise Tests |           | $\pm 3\%$ maximum (when a 500V clamp voltage is applied to the power supply and I/O lines) |                                                        |                              |                                  |  |

| Resistance                                                                                          | e Recommended Cable<br>for Noise Immunity                       |           | Twisted pair shie                                                                          | Ided cable                                             |                              | Twisted pair cable               |  |

|                                                                                                     | Crosstalk                                                       |           |                                                                                            | No crosstalk because of 1 channel output 2 LSB maximum |                              |                                  |  |

| Isolation                                                                                           |                                                                 |           | Isolated between output and power circuit                                                  |                                                        |                              |                                  |  |

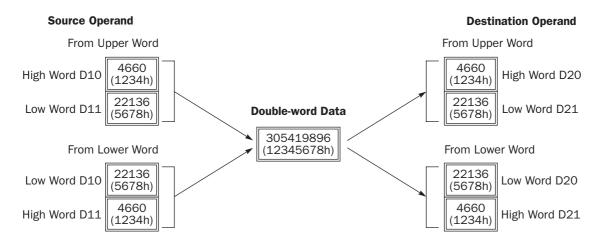

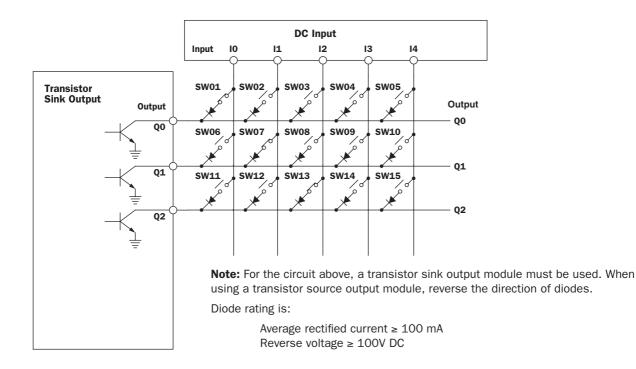

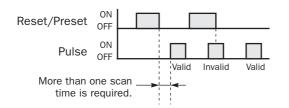

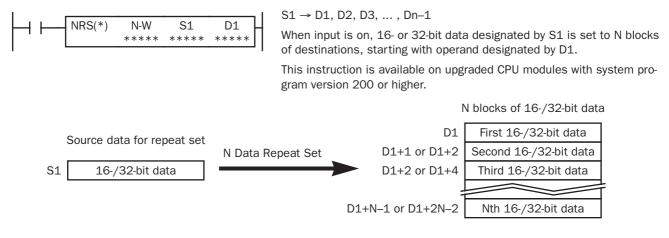

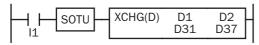

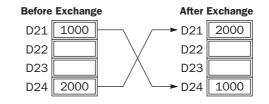

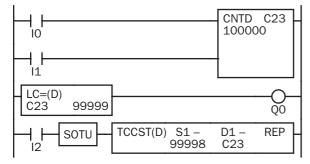

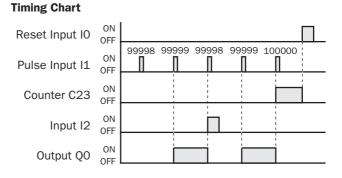

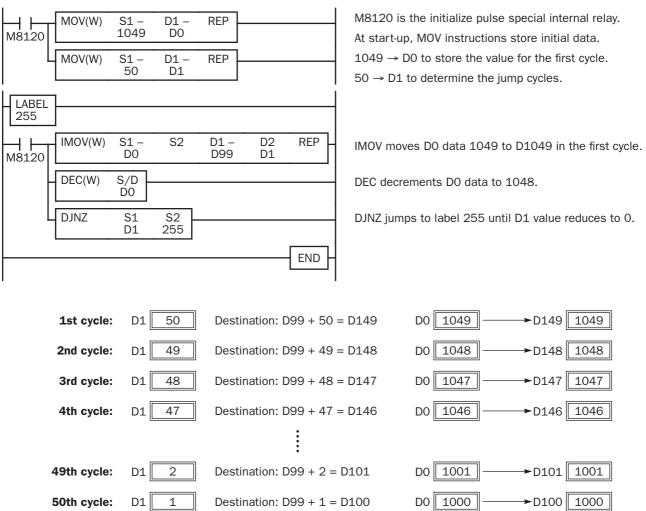

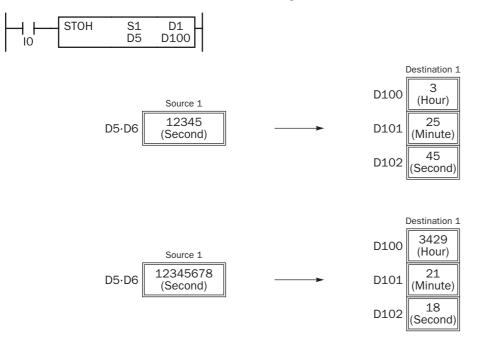

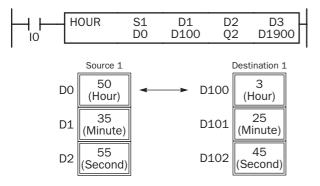

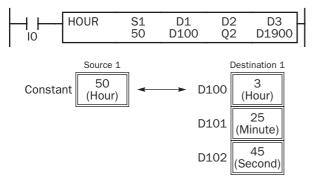

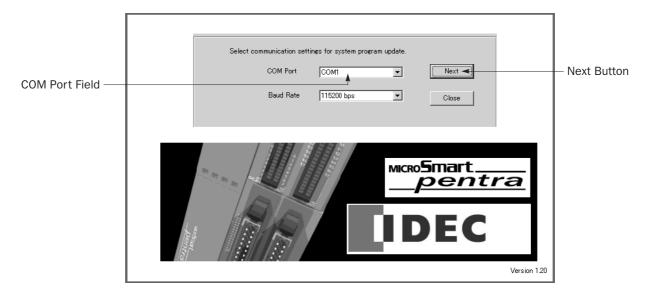

| Isolation                                                                                           |                                                                 |           | Photocoupler-isolated between output and internal circuit                                  |                                                        |                              |                                  |  |