# FC4A SERIES Micro Programmable Logic Controller

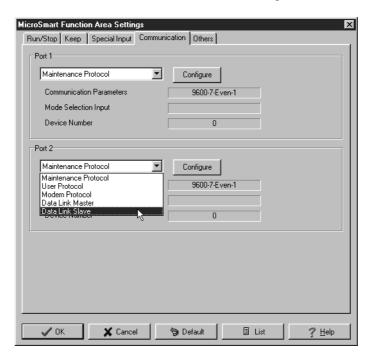

**User's Manual**

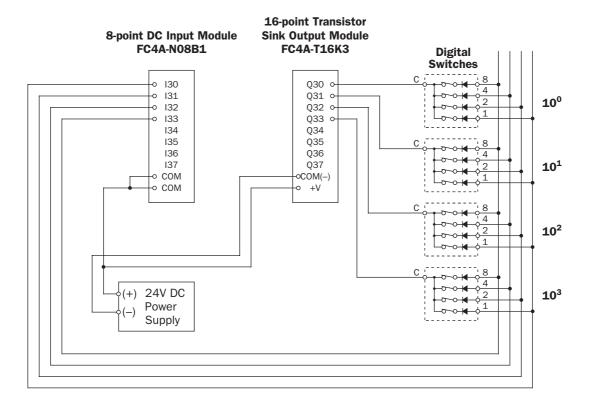

**IDEC CORPORATION**

# MICROSMART USER'S MANUAL UPDATE

## Introduction

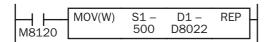

This manual includes additional descriptions of new modules and upgraded functionality of the FC4A MicroSmart CPU modules with system program version up to 210 in detail.

## **New Modules**

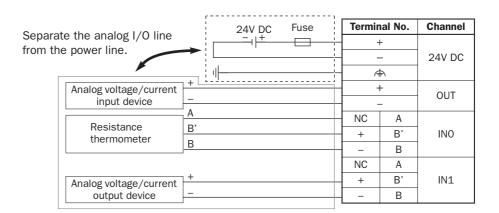

# Analog I/O Modules (Ladder Refresh Type)

| Name                 | 1/0 \$                                                                          | ignal                                             | I/O Points | Type No.   |

|----------------------|---------------------------------------------------------------------------------|---------------------------------------------------|------------|------------|

| Analog Input Module  | Voltage (0 to 10V DC)<br>Thermocouple (K, J, T)<br>Resistance thermometer (Pt10 | Current (4 to 20mA)<br>00, Pt1000, Ni100, Ni1000) | 4 inputs   | FC4A-J4CN1 |

| , maio 8 mpar modalo | Voltage (0 to 10V DC)                                                           | Current (4 to 20mA)                               | 8 inputs   | FC4A-J8C1  |

|                      | Thermistor (NTC, PTC)                                                           |                                                   | 8 inputs   | FC4A-J8AT1 |

| Analog Output Module | Voltage (-10 to +10V DC)                                                        | Current (4 to 20mA)                               | 2 outputs  | FC4A-K2C1  |

# **Upgraded Functionality**

Twelve new functions have been implemented in the FC4A MicroSmart CPU modules. Availability of the twelve new functions depends on the model and system program version of the CPU modules as listed below:

|                                                                          |                           | All-in-One Type           |                           | Slim                     | Туре                                                   |

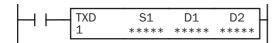

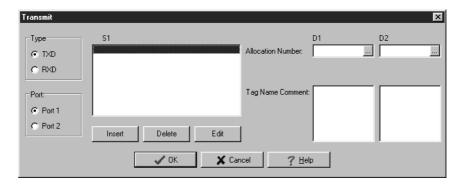

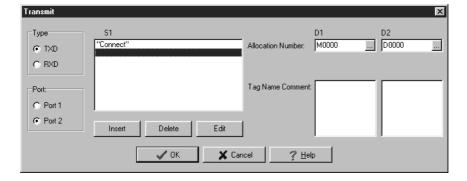

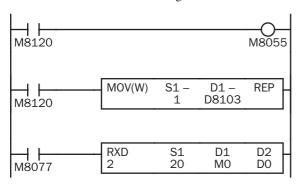

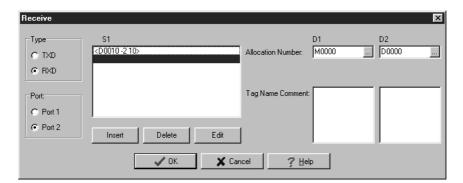

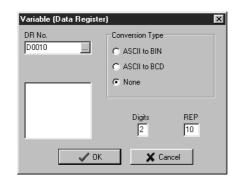

|--------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|--------------------------|--------------------------------------------------------|

| CPU Module                                                               | FC4A-C10R2<br>FC4A-C10R2C | FC4A-C16R2<br>FC4A-C16R2C | FC4A-C24R2<br>FC4A-C24R2C | FC4A-D20K3<br>FC4A-D20S3 | FC4A-D20RK1<br>FC4A-D20RS1<br>FC4A-D40K3<br>FC4A-D40S3 |

| Analog I/O Modules<br>(Ladder Refresh Type)                              | _                         | _                         | 204 or higher             | 204 or higher            | 203 or higher                                          |

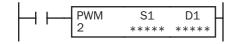

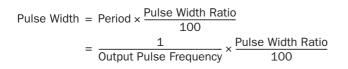

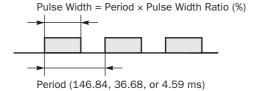

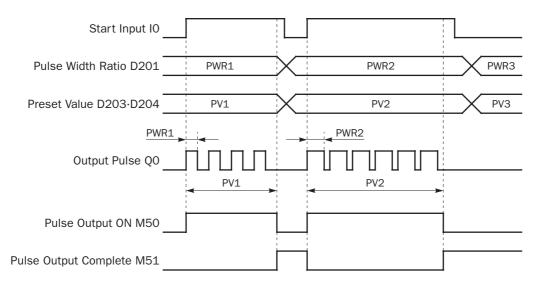

| AS-Interface Master Module Compatibility                                 |                           |                           |                           |                          |                                                        |

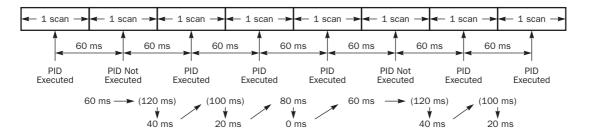

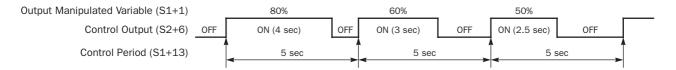

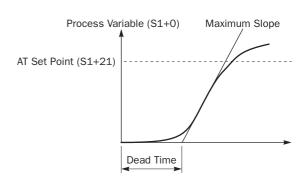

| 64KB Memory Cartridge<br>Compatibility                                   | ] –                       | _                         | _                         | _                        | 201 or higher                                          |

| PID Instruction Upgrade                                                  |                           |                           |                           |                          |                                                        |

| HMI Module Initial Screen Selection                                      | 203 or higher             | 202 or higher             | 202 or higher             | 202 or higher            |                                                        |

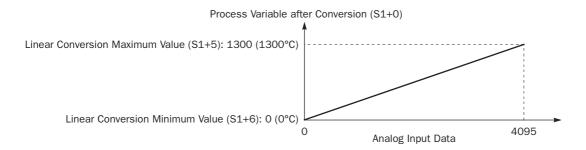

| RS485 User Communication Compatibility                                   |                           |                           |                           |                          |                                                        |

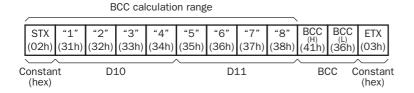

| User Communication BCC Upgrade (ADD-2comp, Modbus ASCII, and Modbus RTU) |                           | 204 or higher             | 204 or higher             | 204 or higher            | 202 or higher                                          |

| Pulse Instructions Upgrade                                               |                           |                           | _                         | 2010111191101            |                                                        |

| Coordinate Conversion<br>Instructions Upgrade                            | _                         | _                         | 204 or higher             |                          | 203 or higher                                          |

| Intelligent Module Access Instructions                                   |                           |                           | 204 of Higher             |                          | 203 of Higher                                          |

| Downloading from Memory<br>Cartridge to CPU Module                       |                           | 210 or higher             | 210 or higher             | 210 or higher            | 210 or higher                                          |

| User Program Read Prohibit                                               |                           |                           |                           |                          |                                                        |

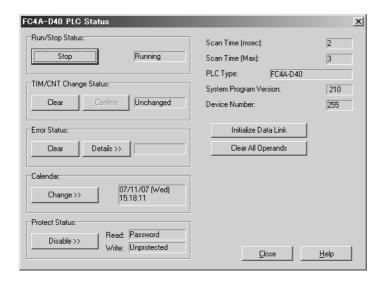

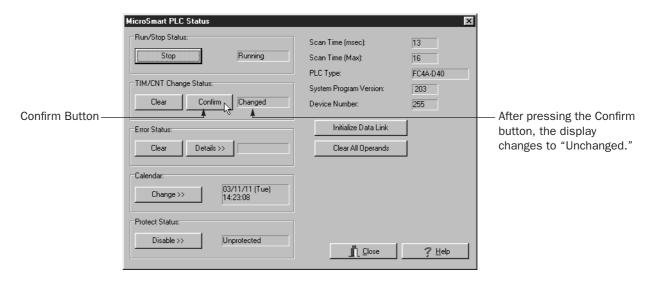

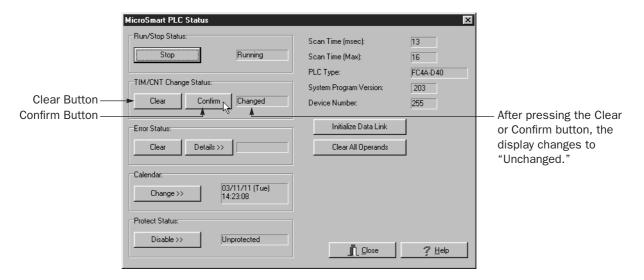

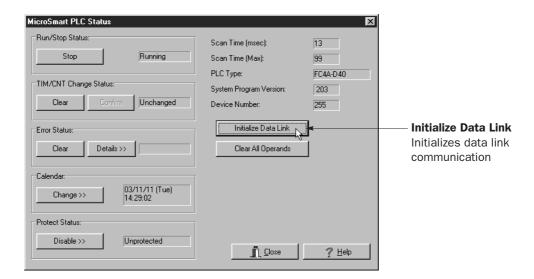

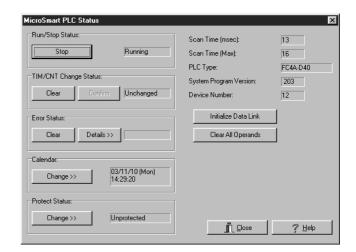

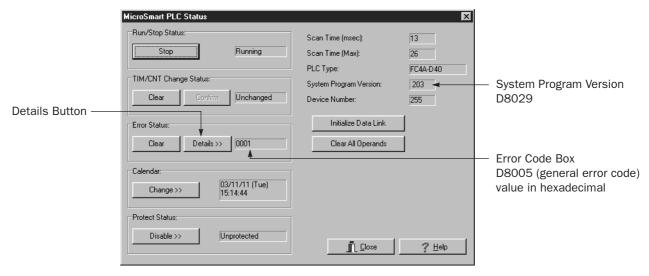

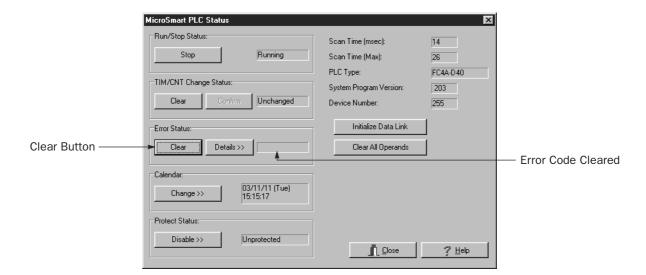

To confirm the system program version of the MicroSmart CPU module, use WindLDR on a computer connected with the CPU module. Bring WindLDR into the online mode. The system program version is indicated on the PLC status dialog box. For details about the procedure, see page 29-1.

# SAFETY PRECAUTIONS

- Read this user's manual to make sure of correct operation before starting installation, wiring, operation, maintenance, and inspection of the MicroSmart.

- All MicroSmart modules are manufactured under IDEC's rigorous quality control system, but users must add a backup or failsafe provision to the control system when using the MicroSmart in applications where heavy damage or personal injury may be caused in case the MicroSmart should fail.

- In this user's manual, safety precautions are categorized in order of importance to Warning and Caution:

Warning notices are used to emphasize that improper operation may cause severe personal injury or death.

- Turn off power to the MicroSmart before starting installation, removal, wiring, maintenance, and inspection of the MicroSmart. Failure to turn power off may cause electrical shocks or fire hazard.

- Special expertise is required to install, wire, program, and operate the MicroSmart. People without such expertise must not use the MicroSmart.

- Emergency stop and interlocking circuits must be configured outside the MicroSmart. If such a circuit is configured inside the MicroSmart, failure of the MicroSmart may cause disorder of the control system, damage, or accidents.

- Install the MicroSmart according to the instructions described in this user's manual. Improper installation will result in falling, failure, or malfunction of the MicroSmart.

Caution notices are used where inattention might cause personal injury or damage to equipment.

- The MicroSmart is designed for installation in a cabinet. Do not install the MicroSmart outside a cabinet.

- Install the MicroSmart in environments described in this user's manual. If the MicroSmart is used in places where the MicroSmart is subjected to high-temperature, high-humidity, condensation, corrosive gases, excessive vibrations, and excessive shocks, then electrical shocks, fire hazard, or malfunction will result.

- The environment for using the MicroSmart is "Pollution degree 2." Use the MicroSmart in environments of pollution degree 2 (according to IEC 60664-1).

- Prevent the MicroSmart from falling while moving or transporting the MicroSmart, otherwise damage or malfunction of the MicroSmart will result.

- Prevent metal fragments and pieces of wire from dropping inside the MicroSmart housing. Put a cover on the MicroSmart modules during installation and wiring. Ingress of such fragments and chips may cause fire hazard, damage, or malfunction.

- Use a power supply of the rated value. Use of a wrong power supply may cause fire hazard.

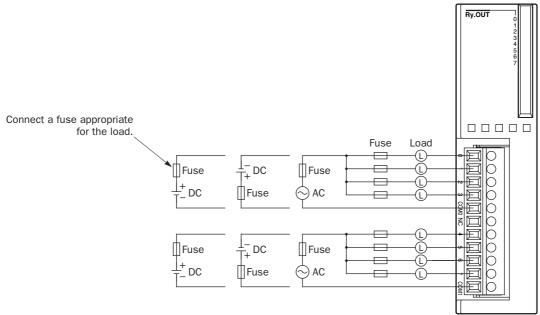

- Use an IEC 60127-approved fuse on the power line outside the MicroSmart. This is required when equipment containing the MicroSmart is destined for Europe.

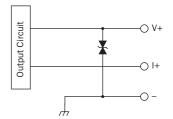

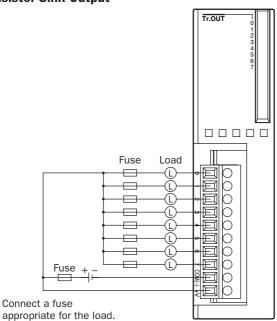

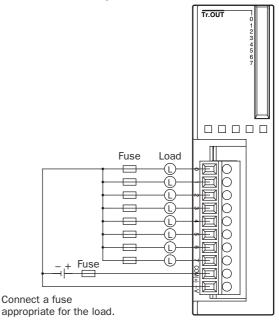

- Use an IEC 60127-approved fuse on the output circuit. This is required when equipment containing the MicroSmart is destined for Europe.

- Use an EU-approved circuit breaker. This is required when equipment containing the MicroSmart is destined for Europe.

- Make sure of safety before starting and stopping the MicroSmart or when operating the MicroSmart to force outputs on or off. Incorrect operation on the MicroSmart may cause machine damage or accidents.

- If relays or transistors in the MicroSmart output modules should fail, outputs may remain on or off. For output signals which may cause heavy accidents, provide a monitor circuit outside the MicroSmart.

- Do not connect the ground wire directly to the MicroSmart. Connect a protective ground to the cabinet containing the MicroSmart using an M4 or larger screw. This is required when equipment containing the MicroSmart is destined for Europe.

- Do not disassemble, repair, or modify the MicroSmart modules.

- Dispose of the battery in the MicroSmart modules when the battery is dead in accordance with pertaining regulations. When storing or disposing of the battery, use a proper container prepared for this purpose. This is required when equipment containing the MicroSmart is destined for Europe.

- When disposing of the MicroSmart, do so as an industrial waste.

#### **About This Manual**

This user's manual primarily describes entire functions, installation, and programming of the FC4A MicroSmart CPU and all other modules. Also included are powerful communications of the MicroSmart and troubleshooting procedures.

#### **CHAPTER 1: GENERAL INFORMATION**

General information about the MicroSmart, features, brief description on special functions, and various system setup configurations for communication.

#### **CHAPTER 2: MODULE SPECIFICATIONS**

Specifications of CPU, input, output, mixed I/O, analog I/O, and other optional modules.

# **CHAPTER 3: INSTALLATION AND WIRING**

Methods and precautions for installing and wiring the MicroSmart modules.

## **CHAPTER 4: OPERATION BASICS**

General information about setting up the basic MicroSmart system for programming, starting and stopping MicroSmart operation, and simple operating procedures from creating a user program using WindLDR on a PC to monitoring the MicroSmart operation.

## **CHAPTER 5: SPECIAL FUNCTIONS**

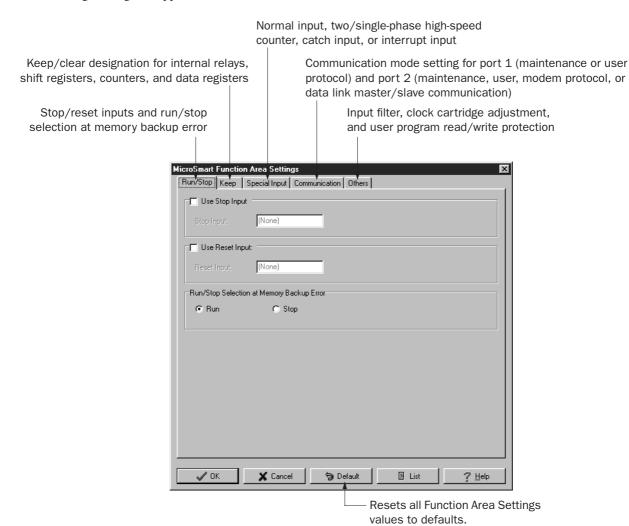

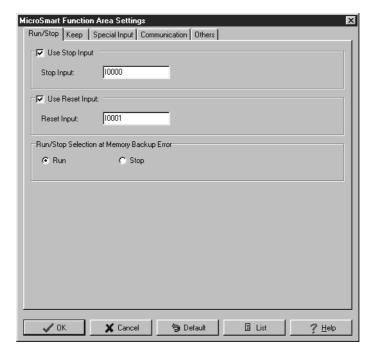

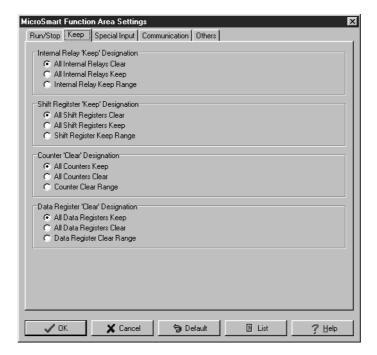

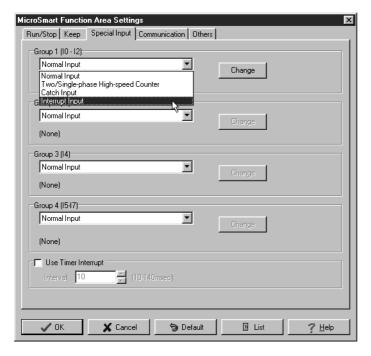

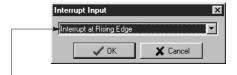

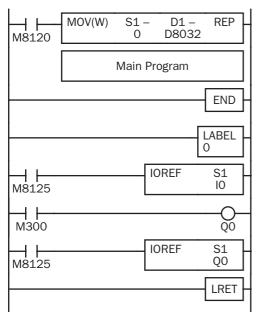

Stop/reset inputs, run/stop selection at memory backup error, keep designation for internal relays, shift registers, counters, and data registers. Also included are high-speed counter, catch input, interrupt input, timer interrupt, input filter, user program read/write protection, constant scan time, partial program download, and many more special functions.

## **CHAPTER 6: ALLOCATION NUMBERS**

Allocation numbers available for the MicroSmart CPU modules to program basic and advanced instructions. Special internal relays and special data registers are also described.

#### **CHAPTER 7: BASIC INSTRUCTIONS**

Programming of the basic instructions, available operands, and sample programs.

# **CHAPTER 8: ADVANCED INSTRUCTIONS**

General rules of using advanced instructions, terms, data types, and formats used for advanced instructions.

# CHAPTER 9 THROUGH CHAPTER 23:

Detailed descriptions on advanced instructions grouped into 15 chapters.

## CHAPTER 24 THROUGH CHAPTER 28:

Analog I/O control and various communication functions such as data link, computer link, modem mode, and AS-Interface.

#### CHAPTER 29: TROUBLESHOOTING

Procedures to determine the cause of trouble and actions to be taken when any trouble occurs while operating the Micro-Smart.

#### **APPENDIX**

Additional information about execution times for instructions, I/O delay time, and MicroSmart type list.

#### INDEX

Alphabetical listing of key words.

# **IMPORTANT INFORMATION**

Under no circumstances shall IDEC Corporation be held liable or responsible for indirect or consequential damages resulting from the use of or the application of IDEC PLC components, individually or in combination with other equipment.

All persons using these components must be willing to accept responsibility for choosing the correct component to suit their application and for choosing an application appropriate for the component, individually or in combination with other equipment.

All diagrams and examples in this manual are for illustrative purposes only. In no way does including these diagrams and examples in this manual constitute a guarantee as to their suitability for any specific application. To test and approve all programs, prior to installation, is the responsibility of the end user.

# **Revision Record**

The table below summarizes the changes to this manual since last printing of FC9Y-B812-0A in June, 2006.

| Revision                                                                 | Description of Change                                                                                    | Page               |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------|

| Analog I/O Modules<br>(Ladder Refresh Type)                              | Four analog input and output modules are added.                                                          | 2-43, 6-5,<br>24-1 |

| AS-Interface Master Module<br>Compatibility                              | AS-Interface master module is added.                                                                     | 2-58, 6-5,<br>28-1 |

| RS485 User Communication<br>Compatibility                                | These functions are now available for FC4A-C16R2, FC4A-C16R2C, FC4A-C24R2C, FC4A-C24R2C, FC4A-D20K3, and | 17-1               |

| User Communication BCC Upgrade (ADD-2comp, Modbus ASCII, and Modbus RTU) | FC4A-D20S3.                                                                                              | 11-1               |

| Pulse Instructions Upgrade                                               | These functions are now available for FC4A-D20K3 and FC4A-D20S3.                                         | 20-1               |

| Coordinate Conversion Instructions Upgrade                               | These functions are now available for FC4A-C24R2C, FC4A-                                                 | 19-1               |

| Intelligent Module Access Instructions                                   | D20K3, and FC4A-D20S3.                                                                                   | 23-1               |

| Downloading from Memory Cartridge to CPU Module                          | A user program can be downloaded from a memory cartridge to the CPU module.                              | 2-66               |

| User Program Read Prohibit                                               | Read protection is upgraded and this option prevents copying of the user program completely.             | 5-25               |

| Analog I/O Modules Upgrade<br>(Version 200 or higher)                    | Four END refresh type analog input and output modules are upgraded.                                      | 2-44               |

# TABLE OF CONTENTS

| Chapter 1:         | GENERAL INFORMATION           About the MicroSmart         1-1           Features         1-1           Special Functions         1-2           System Setup         1-4                                                                                                                                                                                                                                                              |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

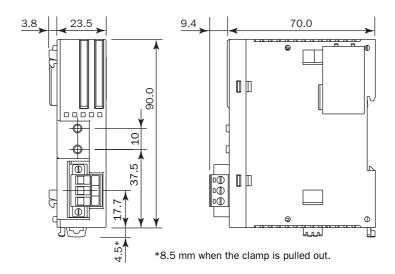

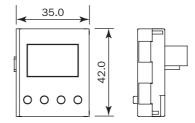

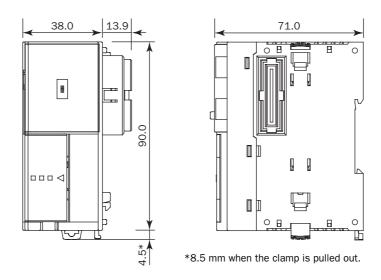

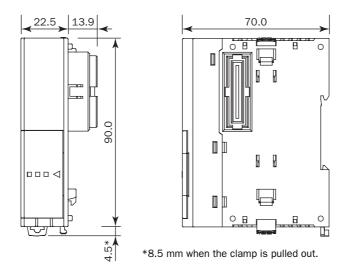

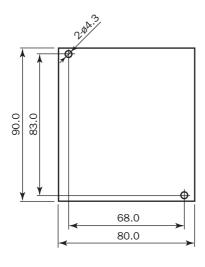

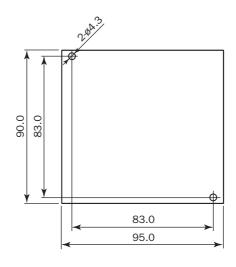

| Chapter 2:         | Module SpecificationsCPU Modules (All-in-One Type)2-1CPU Modules (Slim Type)2-11Input Modules2-23Output Modules2-30Mixed I/O Modules2-39Analog I/O Modules2-43AS-Interface Master Module2-58HMI Module2-60HMI Base Module2-61Communication Adapters and Communication Modules2-62Memory Cartridge2-65Clock Cartridge2-68Dimensions2-69                                                                                                |

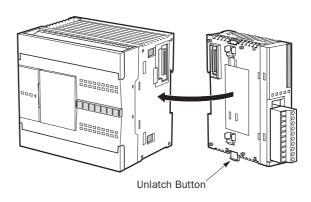

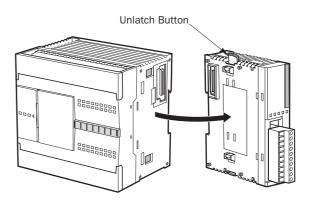

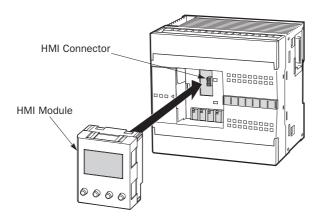

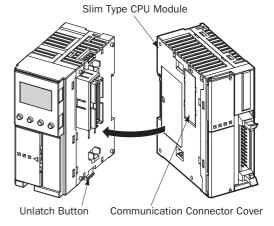

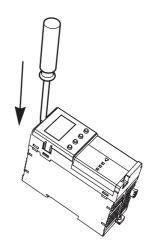

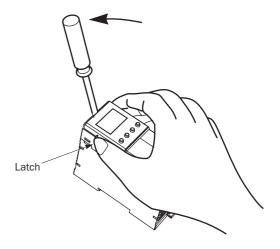

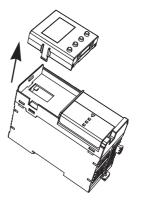

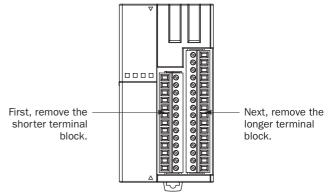

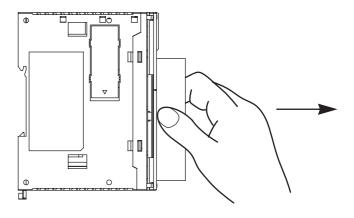

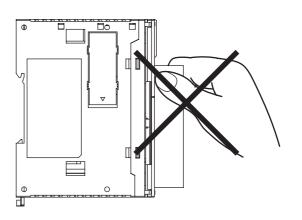

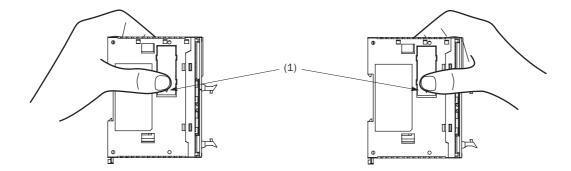

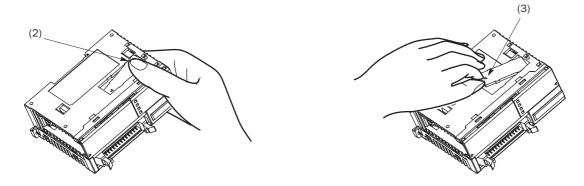

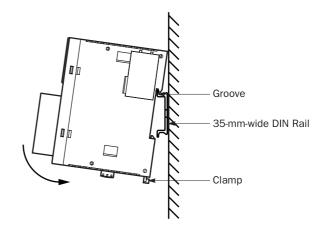

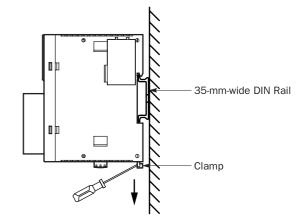

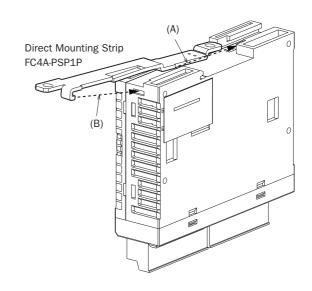

| Chapter 3:         | Installation Location 3-1 Assembling Modules 3-2 Disassembling Modules 3-3 Installing the HMI Module 3-3 Removing the HMI Module 3-4 Removing the Terminal Blocks 3-5 Removing the Communication Connector Cover 3-6 Mounting on DIN Rail 3-7 Removing from DIN Rail 3-7 Direct Mounting on Panel Surface 3-7 Installation in Control Panel 3-11 Mounting Direction 3-12 Input Wiring 3-14 Power Supply 3-16 Terminal Connection 3-18 |

| <b>C</b> HAPTER 4: | OPERATION BASICSConnecting MicroSmart to PC (1:1 Computer Link System)4-1Start/Stop Operation4-3Simple Operation4-5                                                                                                                                                                                                                                                                                                                   |

| CHAPTER 5: | SPECIAL FUNCTIONS                                                                       |

|------------|-----------------------------------------------------------------------------------------|

|            | Function Area Settings                                                                  |

|            | Stop Input and Reset Input                                                              |

|            | Run/Stop Selection at Memory Backup Error                                               |

|            | Keep Designation for Internal Relays, Shift Registers, Counters, and Data Registers 5-4 |

|            | High-speed Counter                                                                      |

|            | Catch Input                                                                             |

|            | Interrupt Input                                                                         |

|            | Timer Interrupt                                                                         |

|            | Input Filter                                                                            |

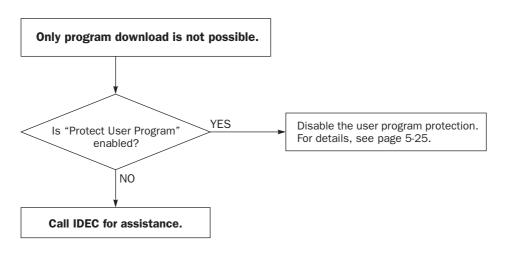

|            | User Program Protection                                                                 |

|            | Constant Scan Time                                                                      |

|            | Partial Program Download                                                                |

|            | Analog Potentiometers                                                                   |

|            | Analog Voltage Input                                                                    |

|            | HMI Module                                                                              |

|            | Expansion Data Registers                                                                |

|            | <u> </u>                                                                                |

| CHAPTER 6: | Allocation Numbers                                                                      |

|            | Operand Allocation Numbers                                                              |

|            | I/O, Internal Relay, and Special Internal Relay Operand Allocation Numbers 6-3          |

|            | Operand Allocation Numbers for END Refresh Type Analog I/O Modules 6-5                  |

|            | Operand Allocation Numbers for AS-Interface Master Module 1 6-5                         |

|            | Operand Allocation Numbers for Data Link Master Station 6-6                             |

|            | Operand Allocation Numbers for Data Link Slave Station 6-6                              |

|            | Special Internal Relays                                                                 |

|            | Special Data Registers                                                                  |

|            | Expansion I/O Module Operands                                                           |

| CHAPTER 7: | Pacio Incerniorione                                                                     |

| CHAPTER 7: | Basic Instructions                                                                      |

|            | Basic Instruction List                                                                  |

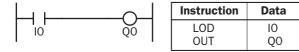

|            | LOD (Load) and LODN (Load Not)                                                          |

|            | OUT (Output) and OUTN (Output Not)                                                      |

|            | SET and RST (Reset)                                                                     |

|            | AND and ANDN (And Not)                                                                  |

|            | OR and ORN (Or Not)                                                                     |

|            | AND LOD (Load)                                                                          |

|            | OR LOD (Load)                                                                           |

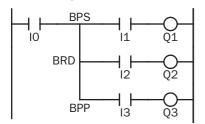

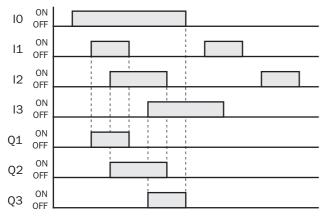

|            | BPS (Bit Push), BRD (Bit Read), and BPP (Bit Pop)                                       |

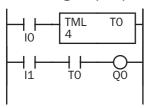

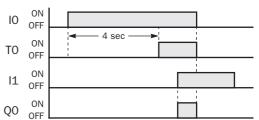

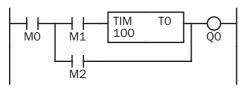

|            | TML, TIM, TMH, and TMS (Timer)                                                          |

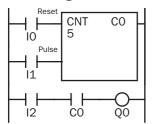

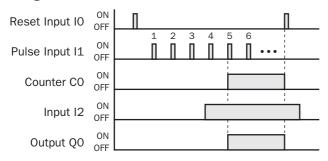

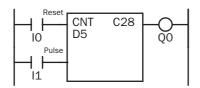

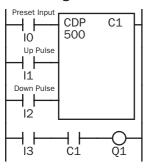

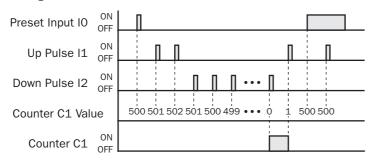

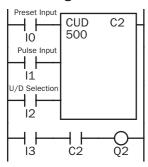

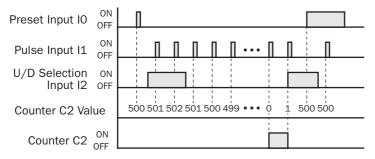

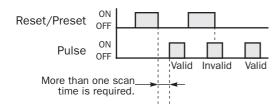

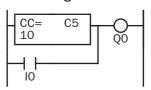

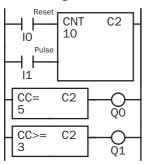

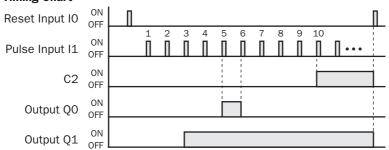

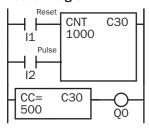

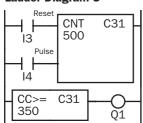

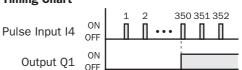

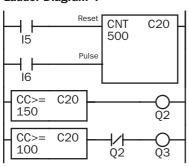

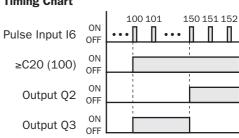

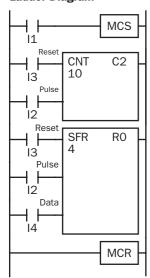

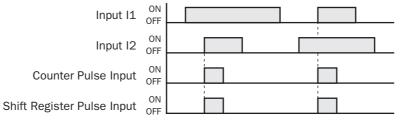

|            | CNT, CDP, and CUD (Counter)                                                             |

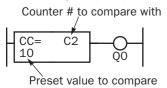

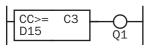

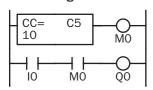

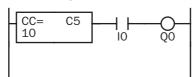

|            | CC= and CC≥ (Counter Comparison)                                                        |

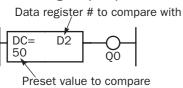

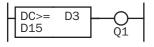

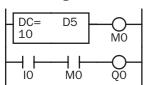

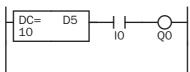

|            | DC= and DC≥ (Data Register Comparison)                                                  |

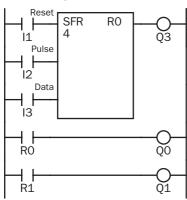

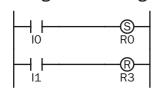

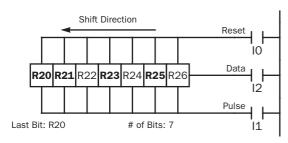

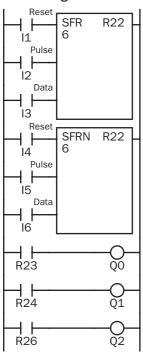

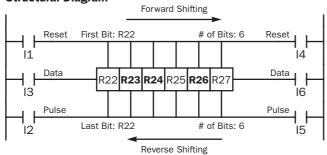

|            | SFR and SFRN (Forward and Reverse Shift Register)                                       |

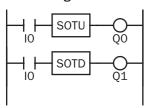

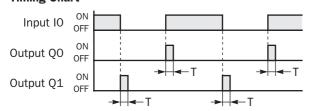

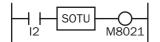

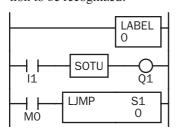

|            | SOTU and SOTD (Single Output Up and Down)                                               |

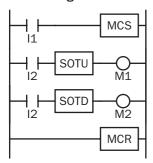

|            | MCS and MCR (Master Control Set and Reset)                                              |

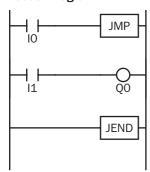

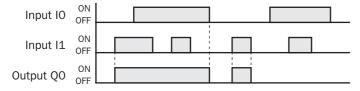

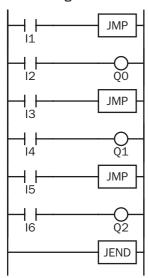

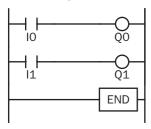

|            | JMP (Jump) and JEND (Jump End)                                                          |

|            | END 7-26                                                                                |

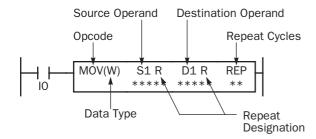

| <b>C</b> HAPTER 8:  | ADVANCED INSTRUCTIONS                              |

|---------------------|----------------------------------------------------|

|                     | Advanced Instruction List                          |

|                     | Structure of an Advanced Instruction               |

|                     | Input Condition for Advanced Instructions 8-       |

|                     | Source and Destination Operands 8-                 |

|                     | Using Timer or Counter as Source Operand           |

|                     | Using Timer or Counter as Destination Operand      |

|                     | Data Types for Advanced Instructions               |

|                     | Discontinuity of Operand Areas                     |

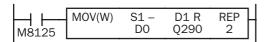

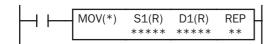

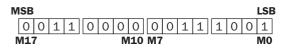

|                     | NOP (No Operation)                                 |

| <b>C</b> HAPTER 9:  | Move Instructions                                  |

|                     | MOV (Move) 9-:                                     |

|                     | MOVN (Move Not)                                    |

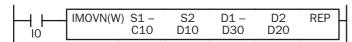

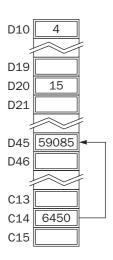

|                     | IMOV (Indirect Move)                               |

|                     | IMOVN (Indirect Move Not)                          |

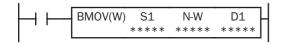

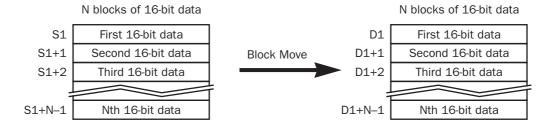

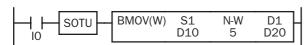

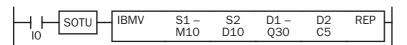

|                     | BMOV (Block Move)                                  |

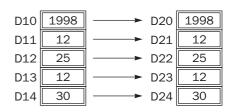

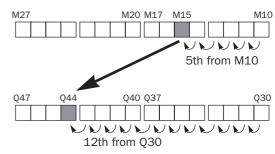

|                     | IBMV (Indirect Bit Move)                           |

|                     | IBMVN (Indirect Bit Move Not)                      |

| <b>C</b> HAPTER 10: | DATA COMPARISON INSTRUCTIONS                       |

|                     | CMP= (Compare Equal To)                            |

|                     | CMP<> (Compare Unequal To)                         |

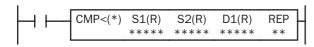

|                     | CMP< (Compare Less Than)                           |

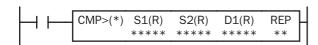

|                     | CMP> (Compare Greater Than)                        |

|                     | CMP<= (Compare Less Than or Equal To)              |

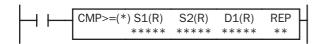

|                     | CMP>= (Compare Greater Than or Equal To)           |

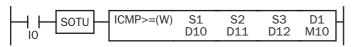

|                     | ICMP>= (Interval Compare Greater Than or Equal To) |

| <b>C</b> HAPTER 11: | BINARY ARITHMETIC INSTRUCTIONS                     |

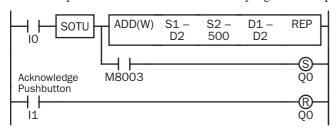

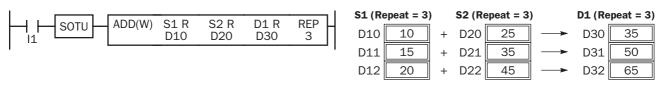

|                     | ADD (Addition)                                     |

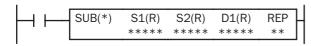

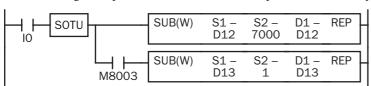

|                     | SUB (Subtraction)                                  |

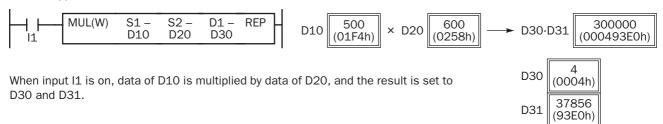

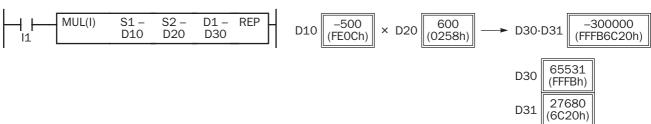

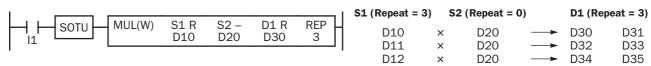

|                     | MUL (Multiplication)                               |

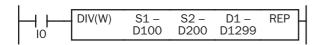

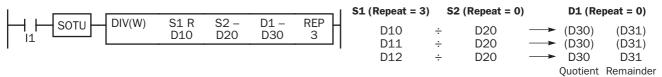

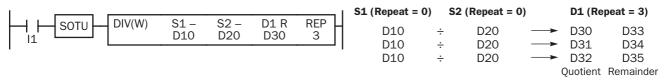

|                     | DIV (Division)                                     |

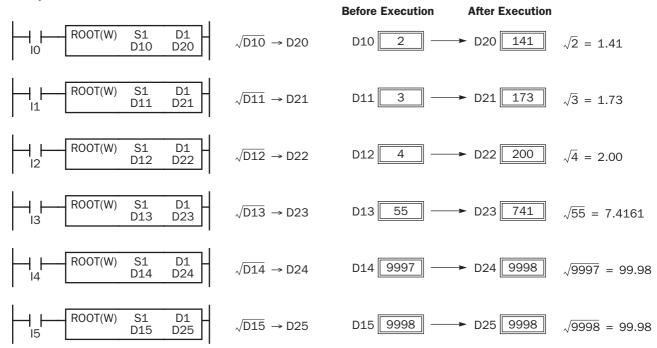

|                     | ROOT (Root)                                        |

| <b>C</b> HAPTER 12: | BOOLEAN COMPUTATION INSTRUCTIONS                   |

|                     | ANDW (AND Word)                                    |

|                     | ORW (OR Word)                                      |

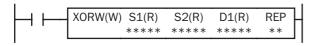

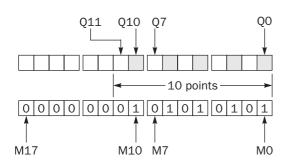

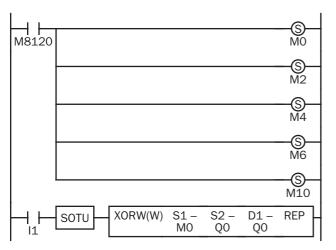

|                     | XORW (Exclusive OR Word)                           |

| <b>C</b> HAPTER 13: | SHIFT / ROTATE INSTRUCTIONS                        |

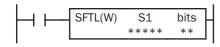

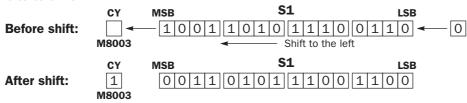

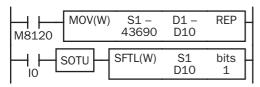

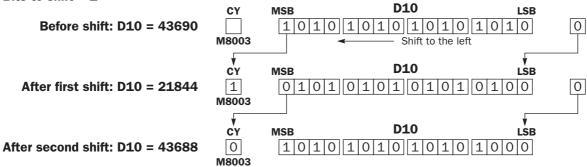

|                     | SFTL (Shift Left)                                  |

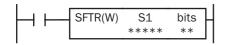

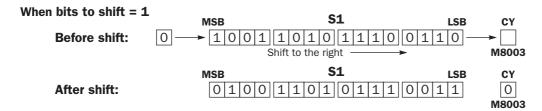

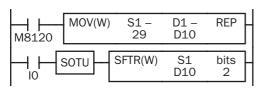

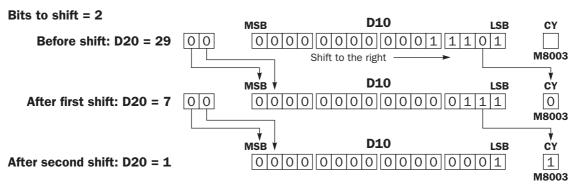

|                     | SFTR (Shift Right)                                 |

|                     | BCDLS (BCD Left Shift)                             |

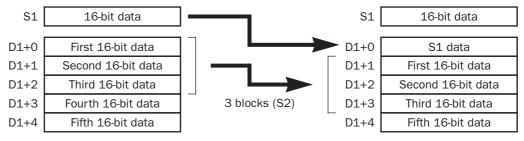

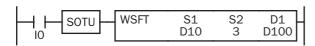

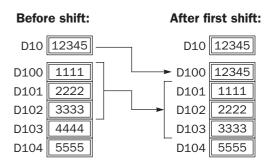

|                     | WSFT (Word Shift)                                  |

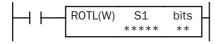

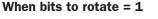

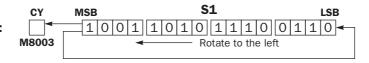

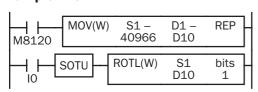

|                     | ROTL (Rotate Left)                                 |

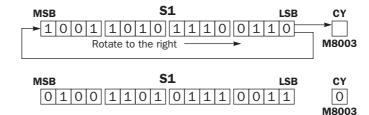

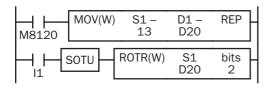

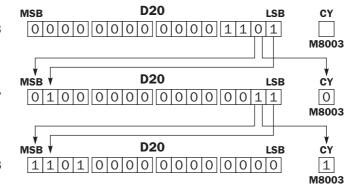

|                     | ROTR (Rotate Right)                                |

| <b>C</b> HAPTER 14: | DATA CONVERSION INSTRUCTIONS                           |

|---------------------|--------------------------------------------------------|

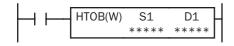

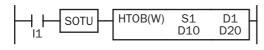

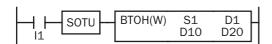

|                     | HTOB (Hex to BCD)                                      |

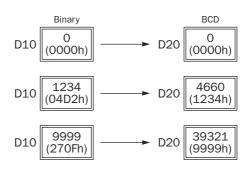

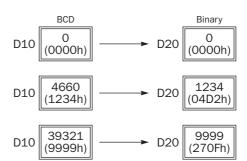

|                     | BTOH (BCD to Hex)                                      |

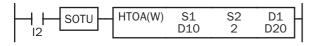

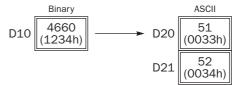

|                     | HTOA (Hex to ASCII)                                    |

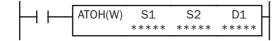

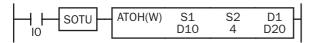

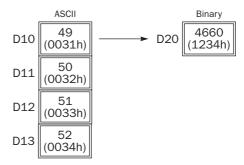

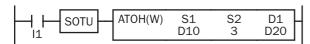

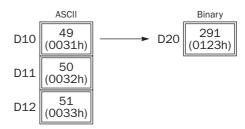

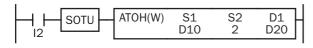

|                     | ATOH (ASCII to Hex)                                    |

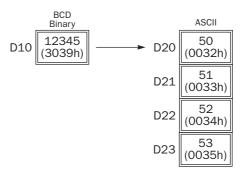

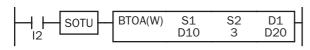

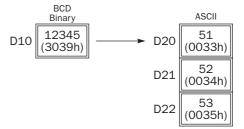

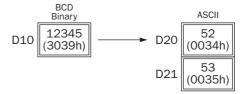

|                     | BTOA (BCD to ASCII)                                    |

|                     | ATOB (ASCII to BCD)                                    |

|                     | ENCO (Encode)                                          |

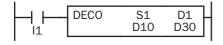

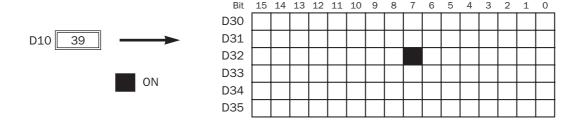

|                     | DECO (Decode)                                          |

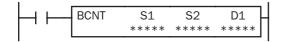

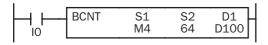

|                     | BCNT (Bit Count)                                       |

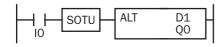

|                     | ALT (Alternate Output)                                 |

| CHAPTER 15:         | Week Programmer Instructions                           |

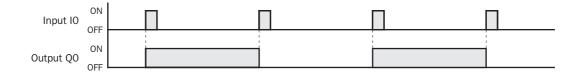

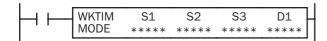

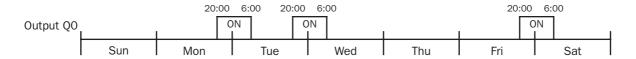

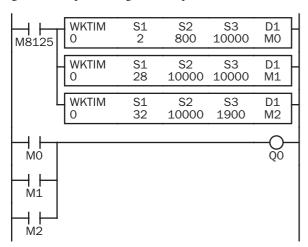

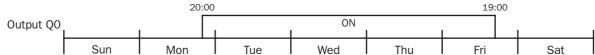

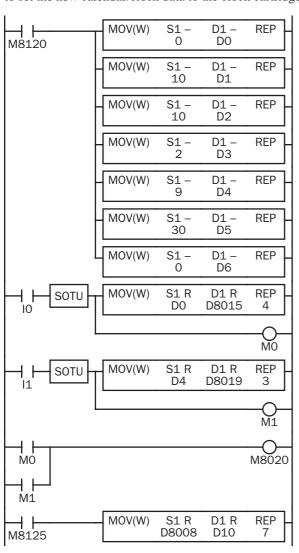

| <u> </u>            | WKTIM (Week Timer)                                     |

|                     | WKTBL (Week Table)                                     |

|                     | Setting Calendar/Clock Using WindLDR                   |

|                     | Setting Calendar/Clock Using a User Program            |

|                     | Adjusting Clock Using a User Program                   |

|                     | Adjusting Clock Cartridge Accuracy                     |

|                     | Adjusting clock cartilage Accuracy                     |

| CHAPTER 16:         | Interface Instructions                                 |

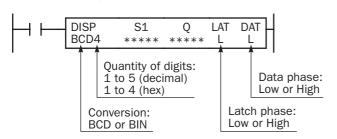

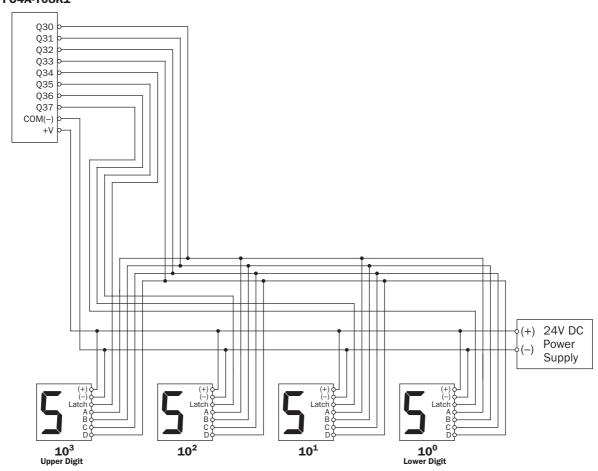

|                     | DISP (Display)                                         |

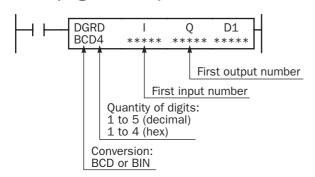

|                     | DGRD (Digital Read)                                    |

| 0                   | Ham Carrennes and Incompany                            |

| <b>C</b> HAPTER 17: | USER COMMUNICATION INSTRUCTIONS                        |

|                     | User Communication Overview                            |

|                     | User Communication Mode Specifications                 |

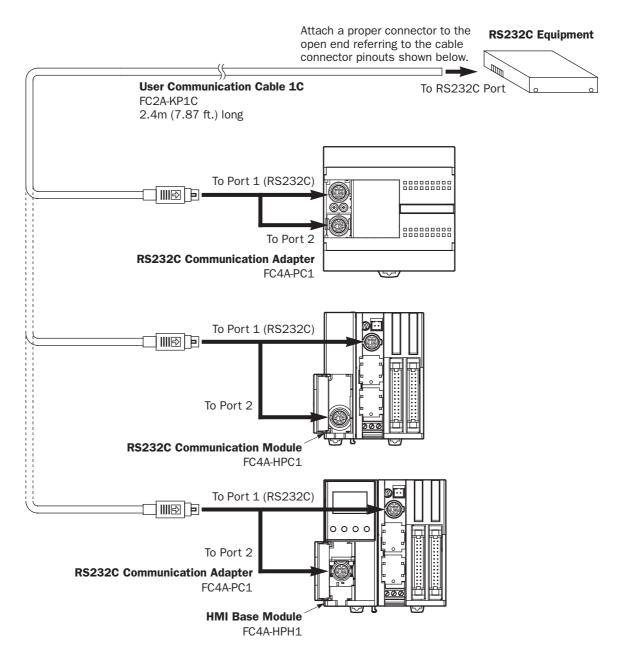

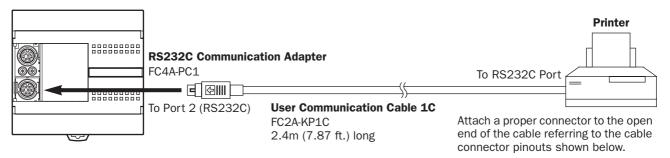

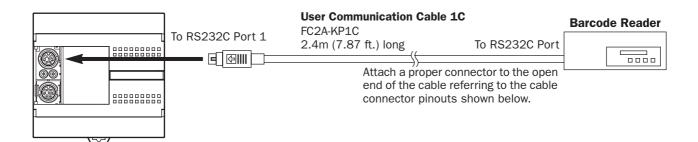

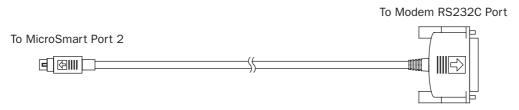

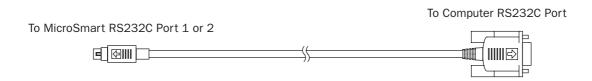

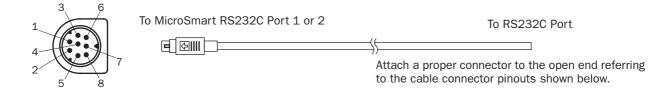

|                     | Connecting RS232C Equipment through RS232C Port 1 or 2 |

|                     | RS232C User Communication System Setup                 |

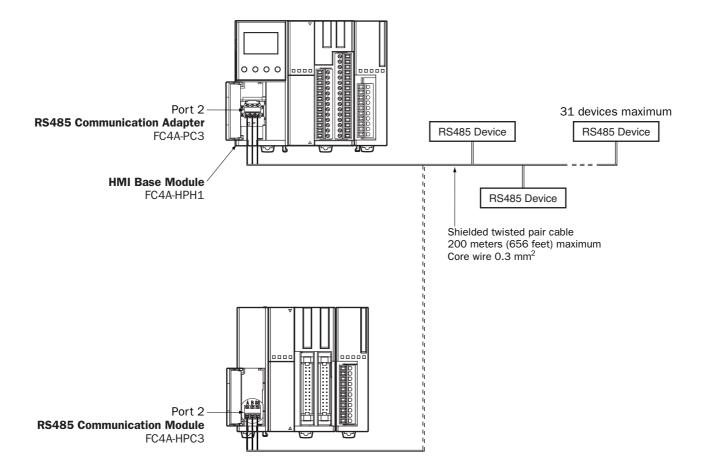

|                     | Connecting RS485 Equipment through RS485 Port 2        |

|                     | RS485 User Communication System Setup                  |

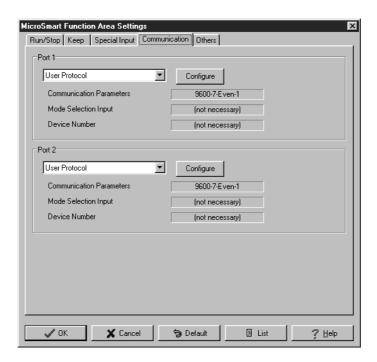

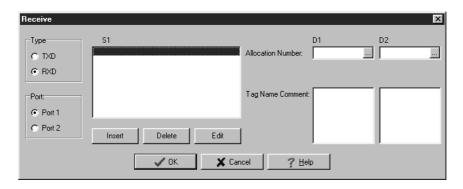

|                     | Programming WindLDR                                    |

|                     | TXD1 (Transmit 1)                                      |

|                     | TXD2 (Transmit 2)                                      |

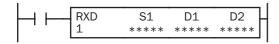

|                     | RXD1 (Receive 1)                                       |

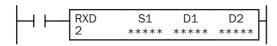

|                     | RXD2 (Receive 2)                                       |

|                     | User Communication Error                               |

|                     | ASCII Character Code Table                             |

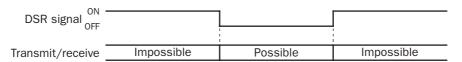

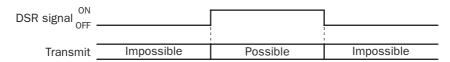

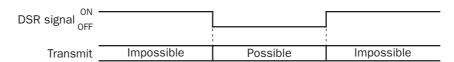

|                     | RS232C Line Control Signals                            |

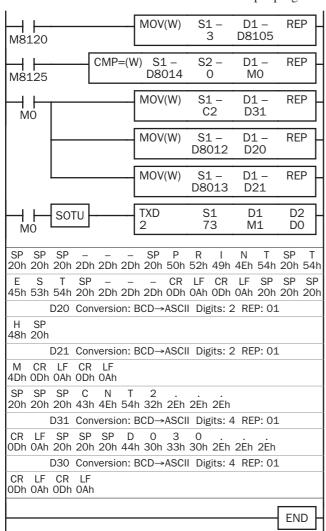

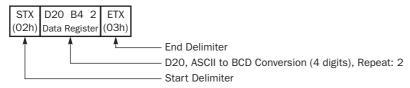

|                     | Sample Program – User Communication TXD                |

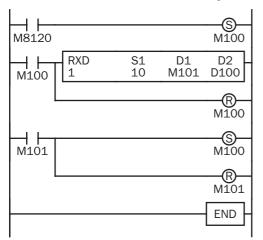

|                     | Sample Program – User Communication RXD                |

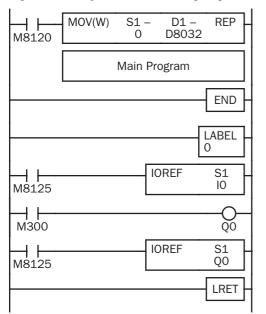

| CHAPTER 18:         | Program Branching Instructions                         |

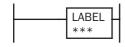

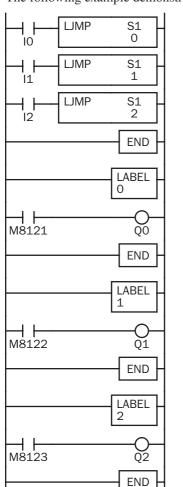

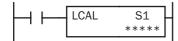

| <u> </u>            | LABEL (Label)                                          |

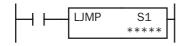

|                     | LJMP (Label Jump)                                      |

|                     | LCAL (Label Call)                                      |

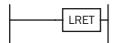

|                     | LRET (Label Return)                                    |

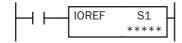

|                     | IOREF (I/O Refresh)                                    |

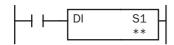

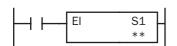

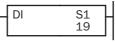

|                     | DI (Disable Interrupt)                                 |

|                     | El (Enable Interrupt)                                  |

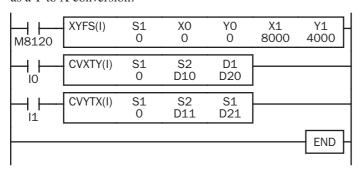

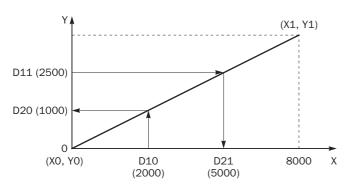

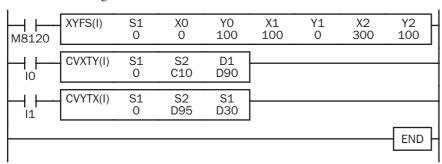

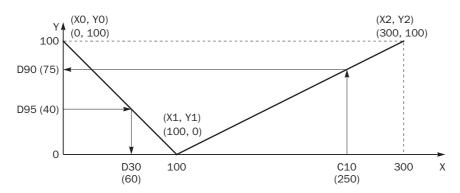

| <b>C</b> HAPTER 19: | COORDINATE CONVERSION INSTRUCTIONS                                                                               |

|---------------------|------------------------------------------------------------------------------------------------------------------|

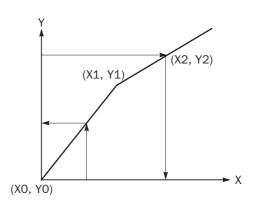

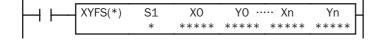

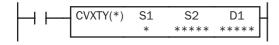

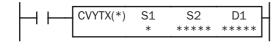

|                     | XYFS (XY Format Set)       19-         CVXTY (Convert X to Y)       19-         CVYTX (Convert Y to X)       19- |

| _                   | CVTIA (Convert 1 to A)                                                                                           |

| <b>C</b> HAPTER 20: | Pulse Instructions                                                                                               |

|                     | PULS1 (Pulse Output 1)       20-         PULS2 (Pulse Output 2)       20-                                        |

|                     | PWM1 (Pulse Width Modulation 1)                                                                                  |

|                     | PWM2 (Pulse Width Modulation 2)                                                                                  |

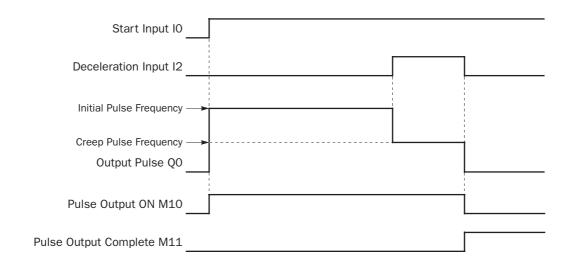

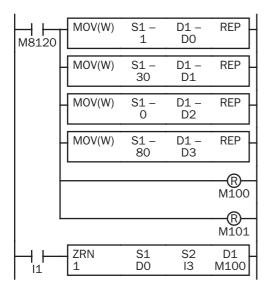

|                     | RAMP (Ramp Control)                                                                                              |

|                     | ZRN1 (Zero Return 1)                                                                                             |

|                     | ZRN2 (Zero Return 2)                                                                                             |

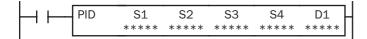

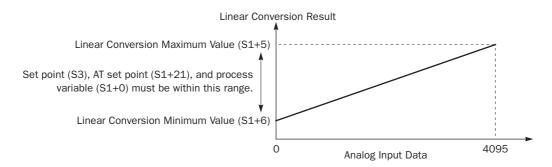

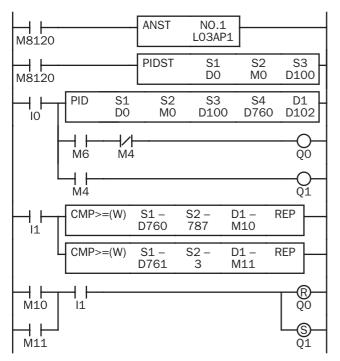

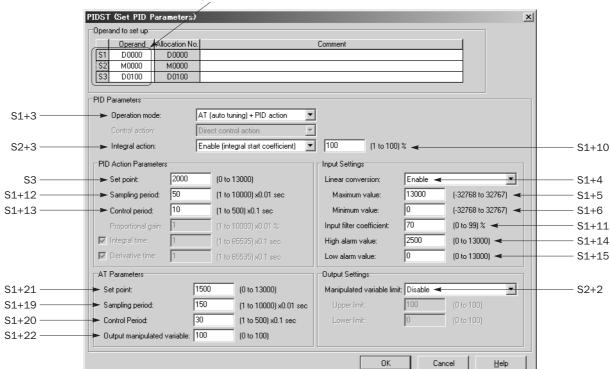

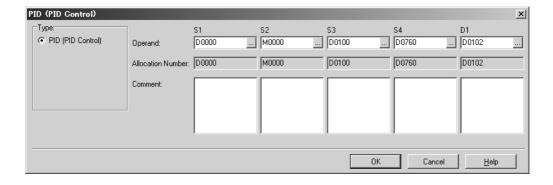

| <b>C</b> HAPTER 21: | PID Instruction                                                                                                  |

|                     | PID (PID Control)                                                                                                |

|                     | Application Example                                                                                              |

| <b>C</b> HAPTER 22: | Dual / Teaching Timer Instructions                                                                               |

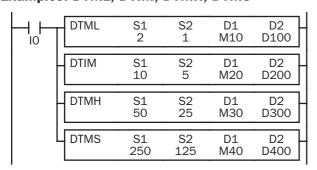

| <u> </u>            | DTML (1-sec Dual Timer)                                                                                          |

|                     | DTIM (100-ms Dual Timer)                                                                                         |

|                     | DTMH (10-ms Dual Timer)                                                                                          |

|                     | DTMS (1-ms Dual Timer)                                                                                           |

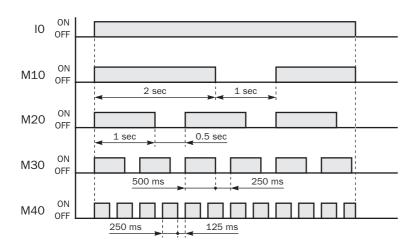

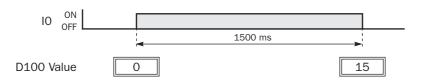

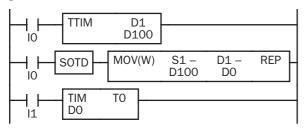

|                     | TTIM (Teaching Timer)                                                                                            |

| <b>C</b> HAPTER 23: | INTELLIGENT MODULE Access Instructions                                                                           |

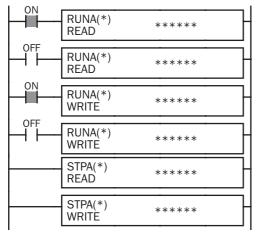

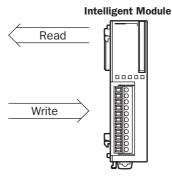

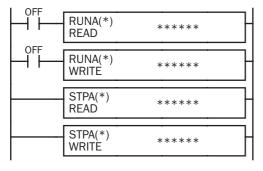

|                     | RUNA READ (Run Access Read)                                                                                      |

|                     | RUNA WRITE (Run Access Write)                                                                                    |

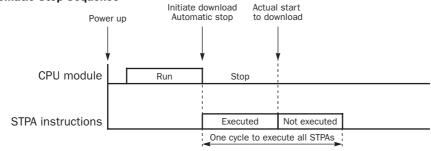

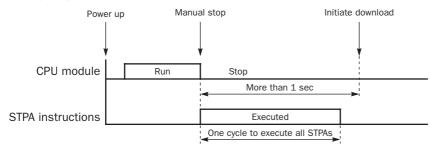

|                     | STPA READ (Stop Access Read)                                                                                     |

|                     | STPA WRITE (Stop Access Write)                                                                                   |

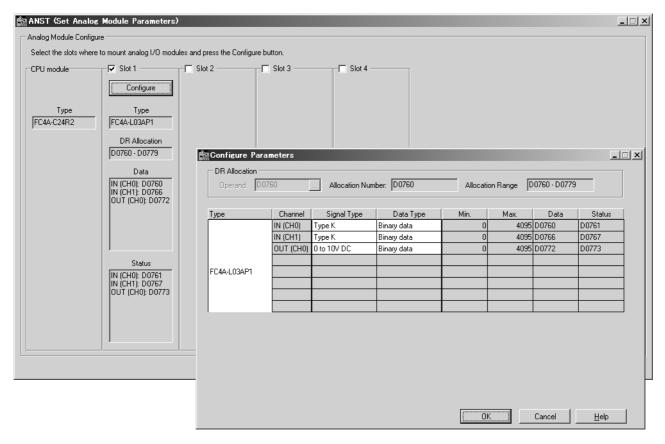

| <b>C</b> HAPTER 24: | Analog I/O Control                                                                                               |

|                     | Applicable CPU Modules                                                                                           |

|                     | System Setup                                                                                                     |

|                     | Programming WindLDR                                                                                              |

|                     | Analog I/O Control Parameters                                                                                    |

|                     | Data Register Allocation Numbers for Analog I/O Modules                                                          |

|                     | Analog Input Parameters                                                                                          |

| 0                   |                                                                                                                  |

| CHAPTER 25:         | DATA LINK COMMUNICATION  Data Link Specifications                                                                |

|                     | Data Link Specifications                                                                                         |

|                     | Data Register Allocation for Transmit/Receive Data                                                               |

|                     | Special Data Registers for Data Link Communication Error                                                         |

|                     | Data Link Communication between Master and Slave Stations                                                        |

|                     | Special Internal Relays for Data Link Communication                                                              |

|                     | Programming WindLDR                                                                                              |

|                     | Refresh Mode                                                                                                     |

|                     | Operating Procedure for Data Link System                                                                         |

|                     | Data Link with Other PLCs                                                                                        |

| CHAPTER 26:         | COMPUTER LINK COMMUNICATION                                                            |     |

|---------------------|----------------------------------------------------------------------------------------|-----|

|                     | Computer Link System Setup (1:N Computer Link System) 2                                | 6-1 |

|                     | Programming WindLDR                                                                    |     |

|                     | Monitoring PLC Status                                                                  |     |

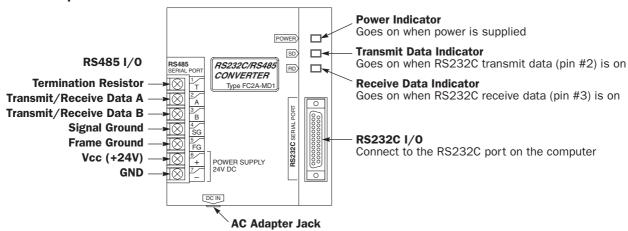

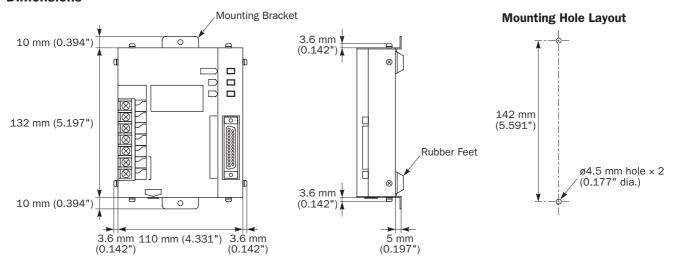

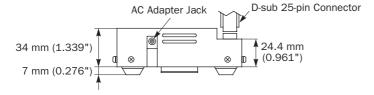

|                     | RS232C/RS485 Converter FC2A-MD1                                                        | 6-4 |

| <b>C</b> HAPTER 27: | MODEM MODE                                                                             |     |

|                     | System Setup                                                                           |     |

|                     | Applicable Modems                                                                      |     |

|                     | Special Internal Relays for Modem Mode                                                 |     |

|                     | Special Data Registers for Modem Mode                                                  |     |

|                     | Originate Mode                                                                         |     |

|                     | Disconnect Mode                                                                        |     |

|                     | AT General Command Mode                                                                |     |

|                     | Answer Mode                                                                            |     |

|                     | Modem Mode Status Data Register       2         Initialization String Commands       2 |     |

|                     | Preparation for Using Modem                                                            |     |

|                     | Programming Data Registers and Internal Relays                                         |     |

|                     | Setting Up the CPU Module                                                              |     |

|                     | Programming WindLDR                                                                    |     |

|                     | Operating Procedure for Modem Mode                                                     |     |

|                     | Sample Program for Modem Originate Mode                                                |     |

|                     | Sample Program for Modem Answer Mode                                                   |     |

|                     | Troubleshooting in Modem Communication                                                 | -14 |

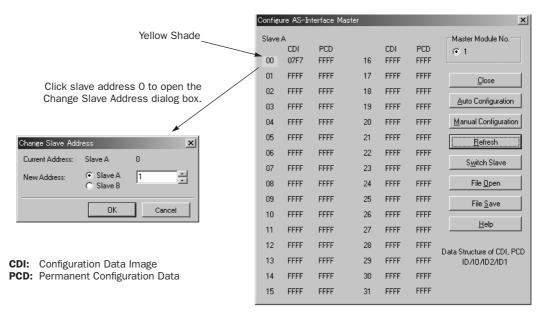

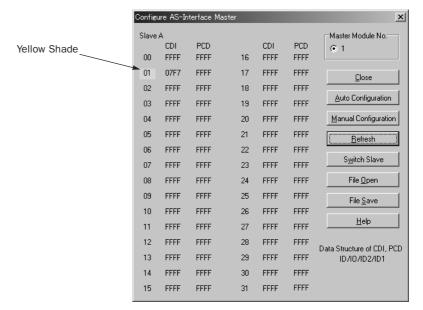

| CHAPTER 28:         | AS-Interface Master Communication                                                      |     |

| OHAI TER ZO.        | About AS-Interface                                                                     | 8-1 |

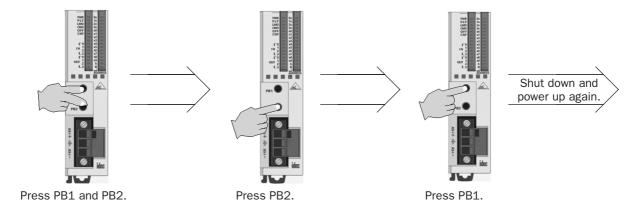

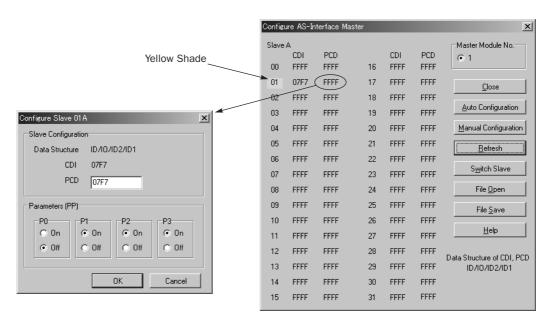

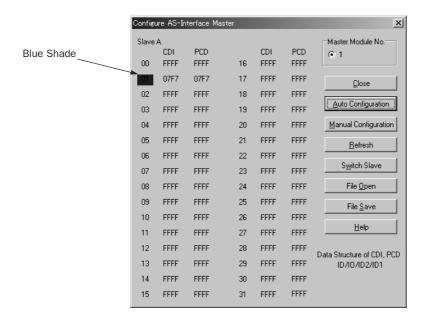

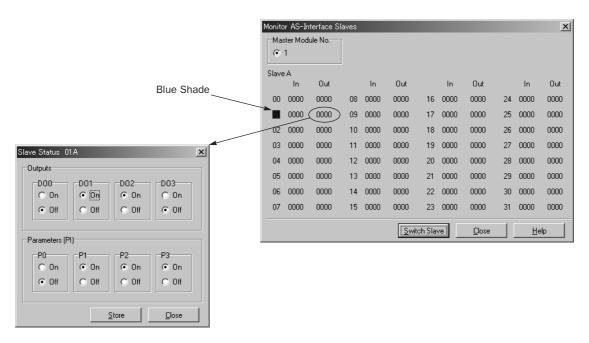

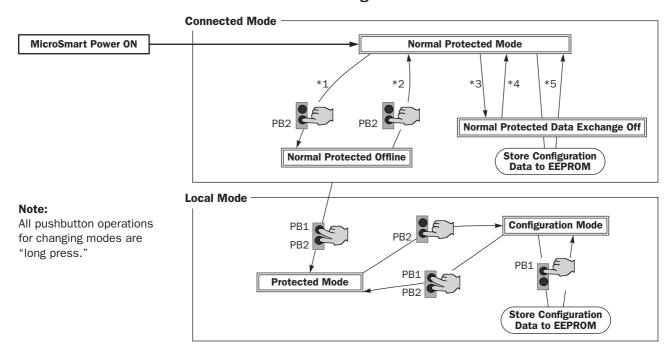

|                     | Operation Basics                                                                       |     |

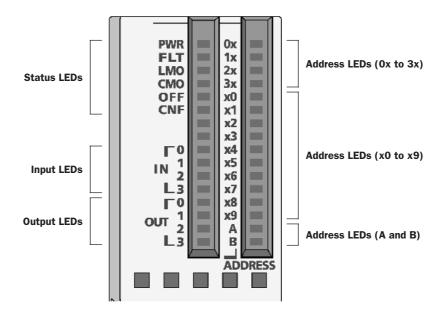

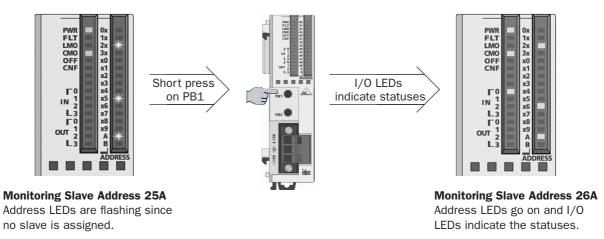

|                     | Pushbuttons and LED Indicators                                                         |     |

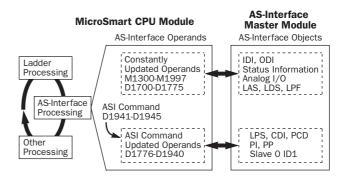

|                     | AS-Interface Operands                                                                  |     |

|                     | Using Two AS-Interface Master Modules                                                  |     |

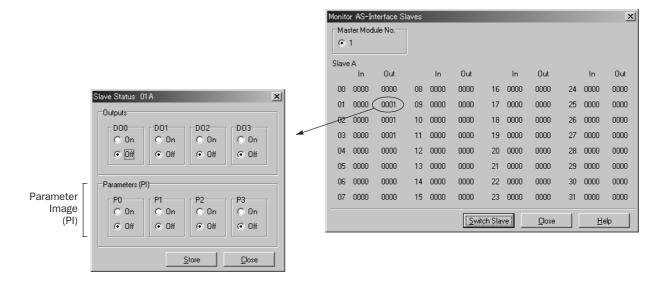

|                     | Using WindLDR 28                                                                       |     |

|                     | SwitchNet Data I/O Port (AS-Interface Master Module 1)                                 |     |

| CHAPTER 29:         | Troubleshooting                                                                        |     |

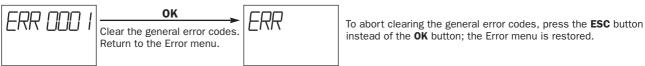

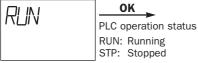

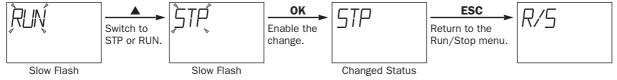

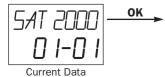

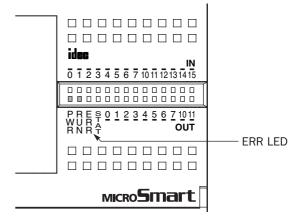

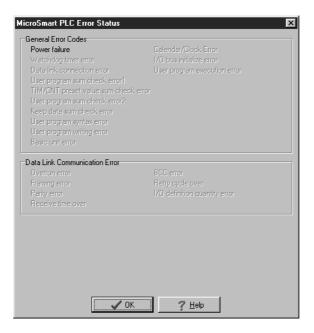

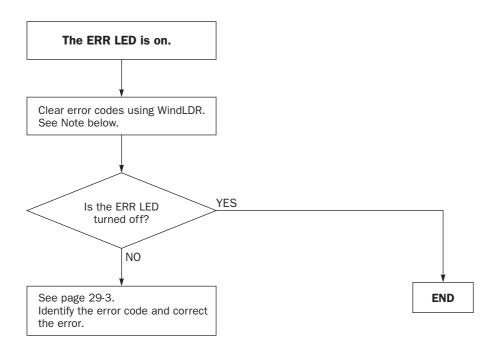

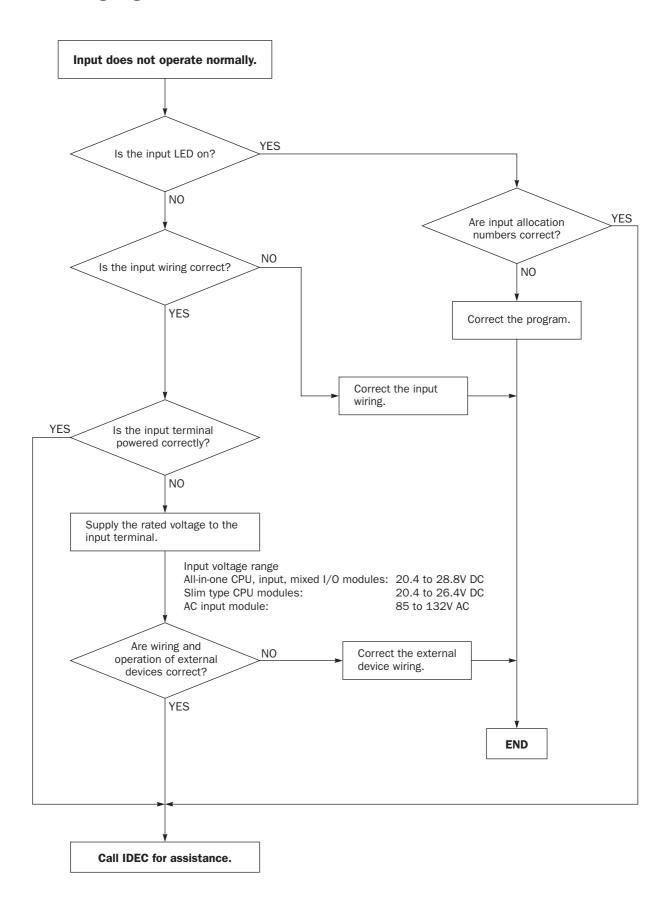

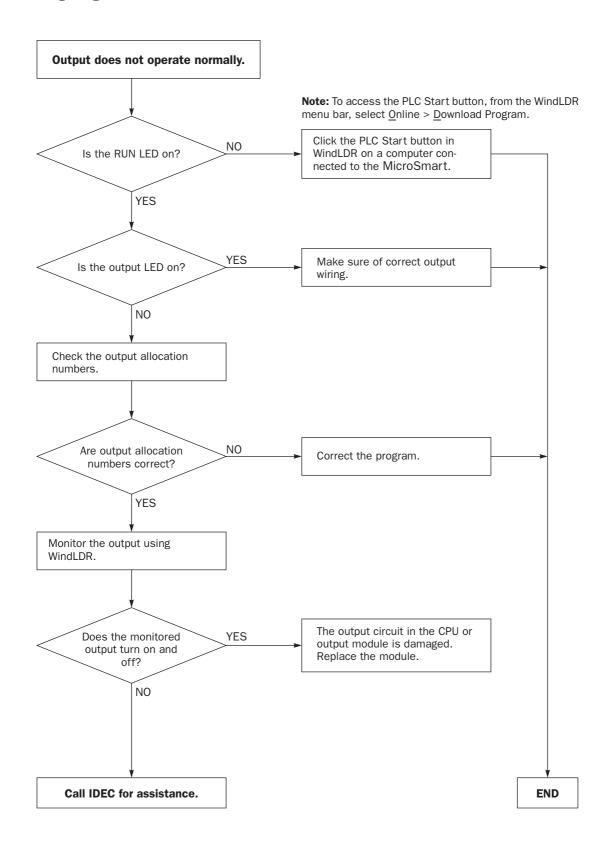

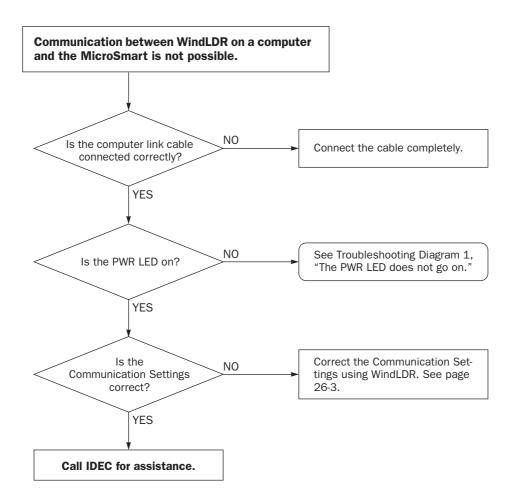

| <u> </u>            | ERR LED                                                                                | 9-1 |

|                     | Reading Error Data                                                                     | 9-1 |

|                     | Special Data Registers for Error Information                                           | 9-3 |

|                     | General Error Codes                                                                    |     |

|                     | CPU Module Operating Status, Output, and ERR LED during Errors                         | 9-4 |

|                     |                                                                                        | 9-4 |

|                     | User Program Execution Error                                                           |     |

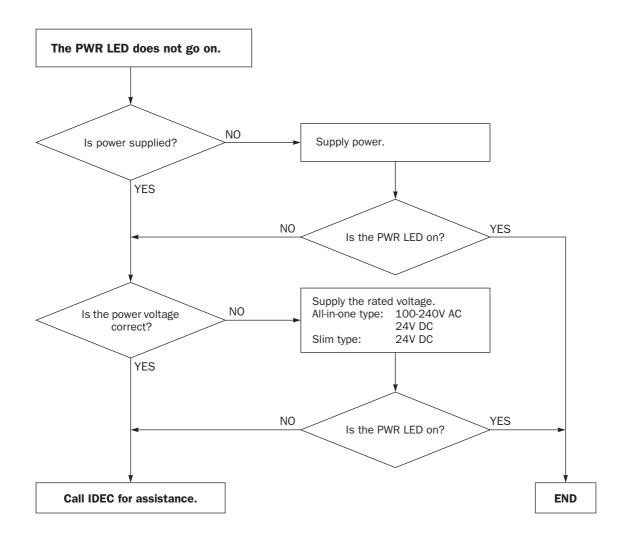

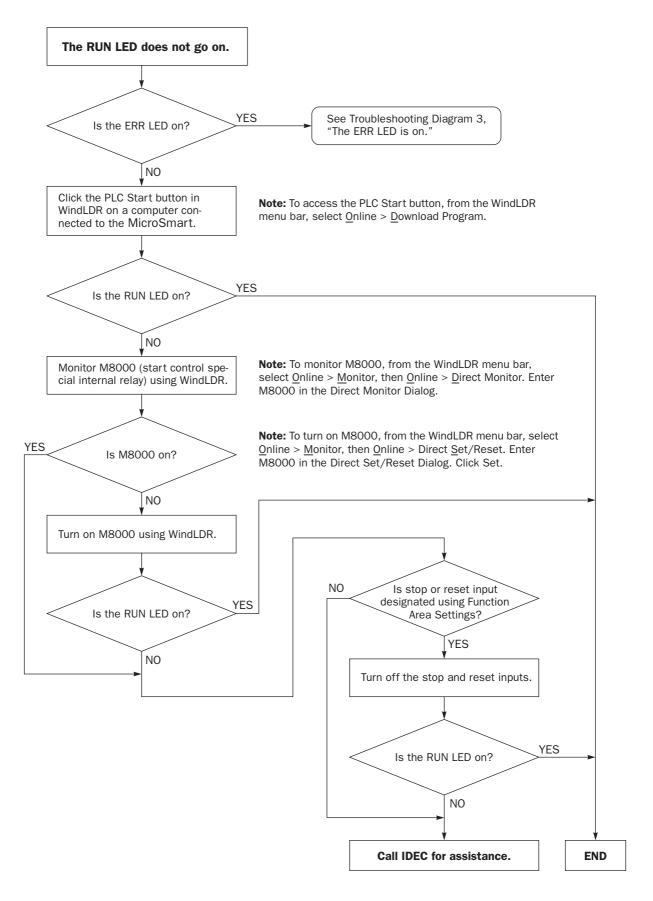

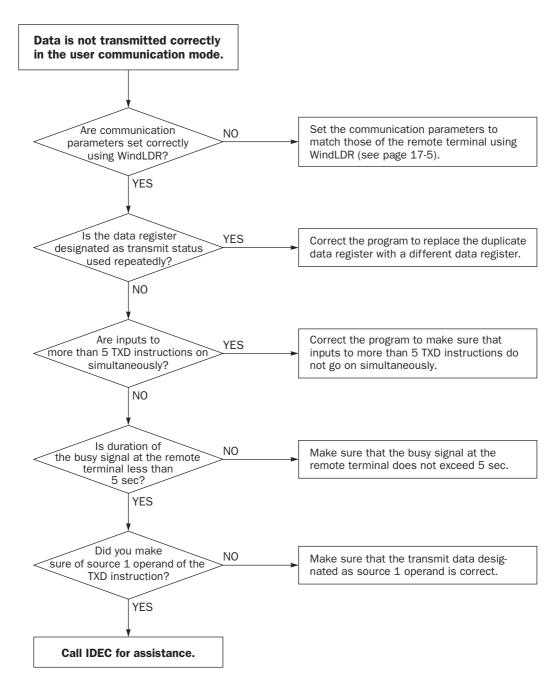

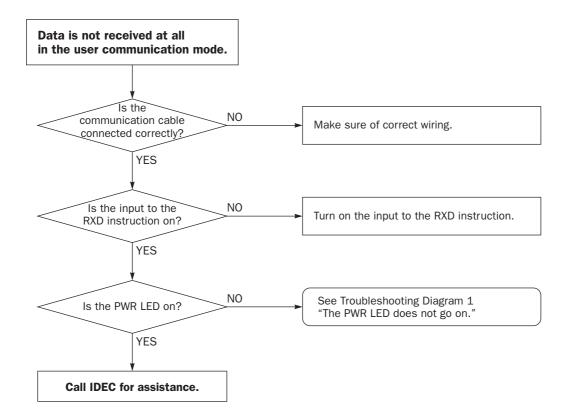

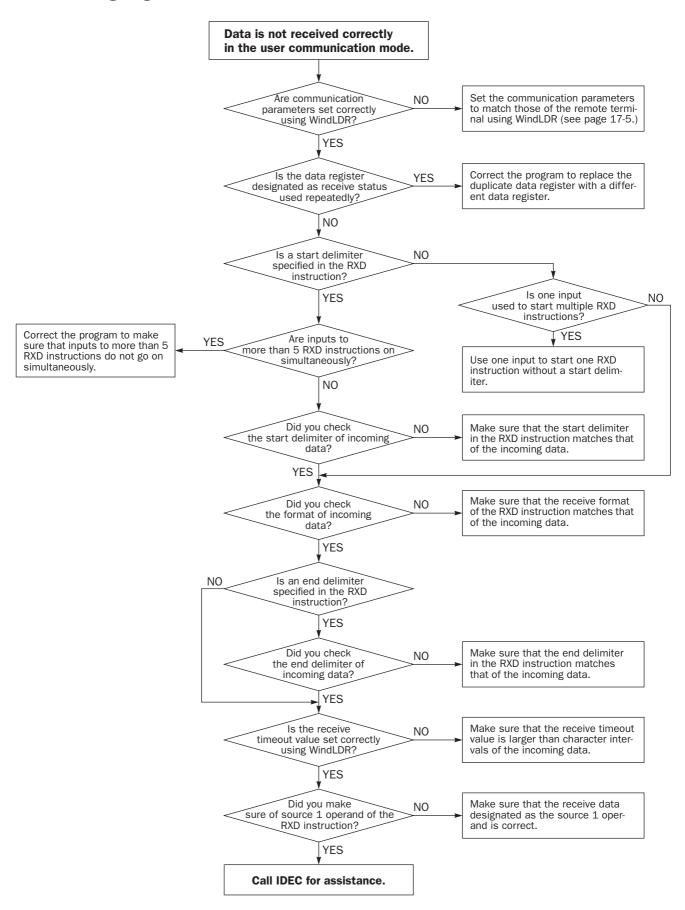

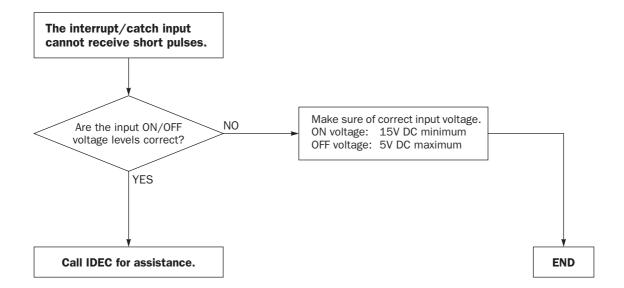

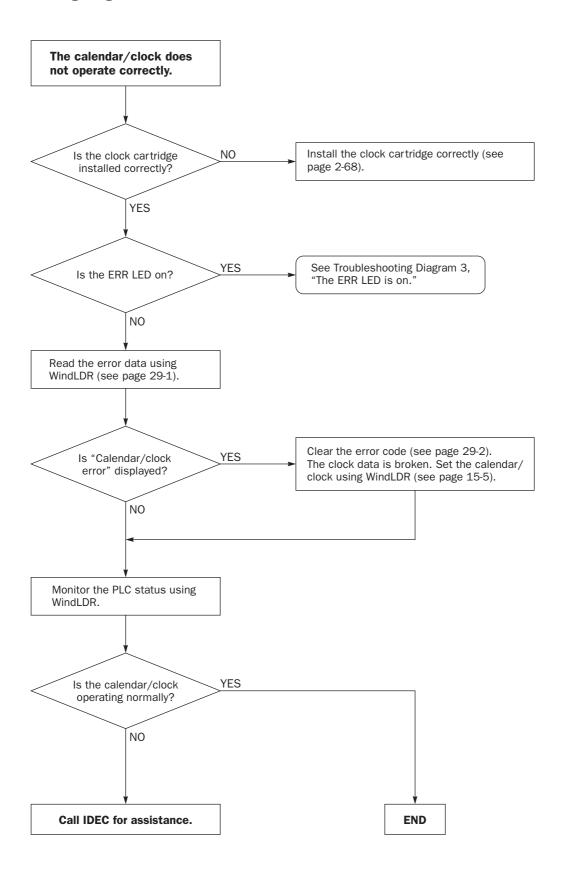

|                     | Troubleshooting Diagrams                                                               |     |

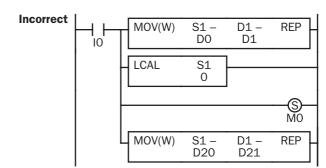

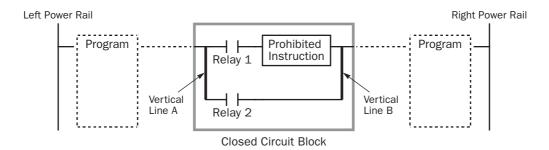

|                     | Restriction on Ladder Programming                                                      | -22 |

| <b>A</b> PPENDIX    | Execution Times for Instructions                                                       | 0-1 |

| - <del></del>       | Breakdown of END Processing Time                                                       |     |

|                     | I/O Delay Time                                                                         |     |

|                     | Instruction Steps and Applicability in Interrupt Programs                              |     |

|                     | Cables 3                                                                               | 0-4 |

|                     | Type List                                                                              | 0-7 |

|                     |                                                                                        |     |

<u>NDEX</u>

# 1: GENERAL INFORMATION

# Introduction

This chapter describes general information for understanding the MicroSmart's powerful capabilities and system setups to use the MicroSmart in various ways of communication.

# **About the MicroSmart**

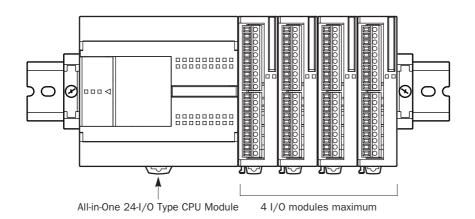

IDEC's MicroSmart is a new family of micro programmable logic controllers available in two styles of CPU modules; all-in-one and slim types. The all-in-one type CPU module has 10, 16, or 24 I/O terminals and is equipped with a built-in universal power supply to operate on 100 to 240V AC or 24V DC. Using four 16-point I/O modules, the 24-I/O type CPU module can expand the I/O points up to a total of 88 points. The slim type CPU module has 20 or 40 I/O terminals and operates on 24V DC. The total I/O points can be expanded to a maximum of 264.

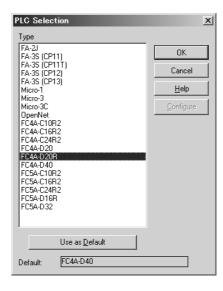

User programs for the MicroSmart can be edited using WindLDR on a Windows PC. Since WindLDR can load existing user programs made for IDEC's previous PLCs such as all FA series, MICRO-1, MICRO<sup>3</sup>C, and OpenNet Controller, your software assets can be used in the new control system.

Program capacity of the all-in-one type CPU modules is 4,800 bytes (800 steps) on the 10-I/O type CPU module, 15,000 bytes (2,500 steps) on the 16-I/O type, and 27,000 bytes (4,500 steps) on the 24-I/O type. Slim type CPU modules have a program capacity of 27,000 bytes (4,500 steps) or 31,200 bytes (5,200 steps). When using an optional 64KB memory cartridge on slim type CPU modules, the program capacity can be expanded up to 64,500 bytes (10,750 steps).

# **Features**

#### **Powerful Communication Functions**

The MicroSmart features four powerful communication functions.

| Maintenance<br>Communication<br>(Computer Link) | When a MicroSmart CPU module is connected to a computer, operating status and I/O status can be monitored on the computer, data in the CPU can be monitored or updated, and user programs can be downloaded and uploaded. All CPU modules (except the all-in-one 10-I/O type) can set up a 1:N computer link system to connect a maximum of 32 CPU modules to a computer. |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| User Communication                              | All MicroSmart CPU modules can be linked to external RS232C devices such as computers, printers, and barcode readers, using the user communication function. RS485 user communication is also available on upgraded CPU modules of slim 20-I/O relay output and 40-I/O types.                                                                                             |

| Modem Communication                             | All MicroSmart CPU modules (except the all-in-one 10-I/O type) can communicate through modems using the built-in modem protocol.                                                                                                                                                                                                                                          |

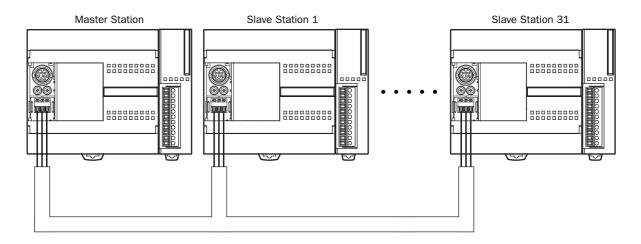

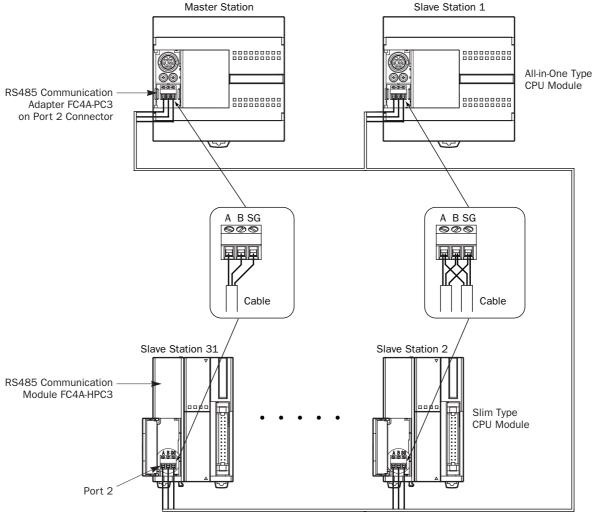

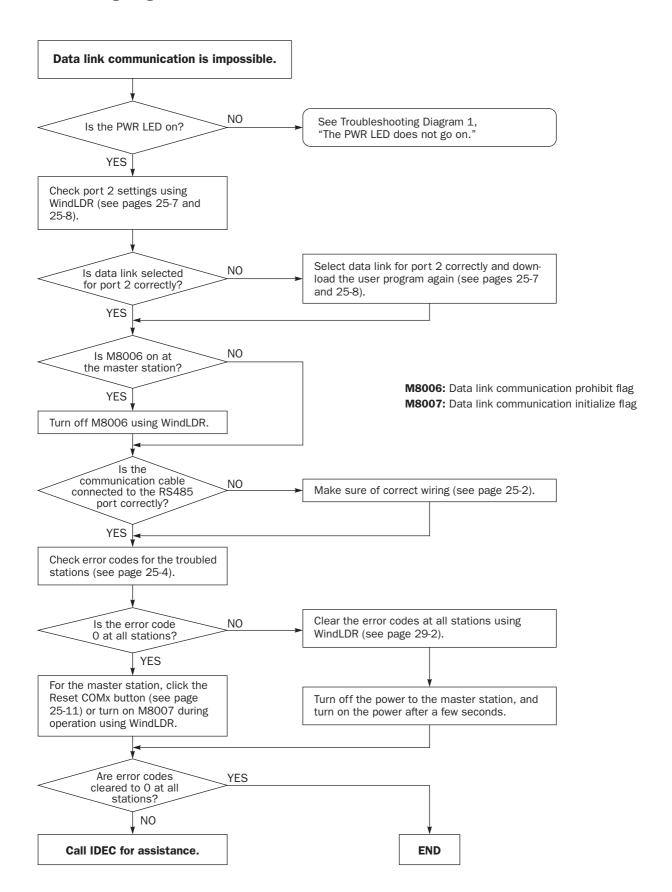

| Data Link                                       | All MicroSmart CPU modules (except the all-in-one 10-I/O type) can set up a data link system. One CPU module at the master station can communicate with 31 slave stations through an RS485 line to exchange data and perform distributed control effectively.                                                                                                             |

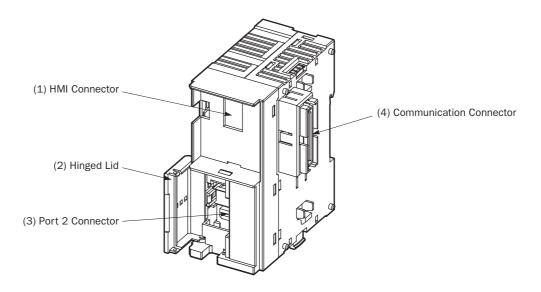

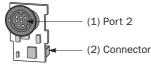

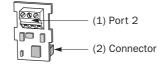

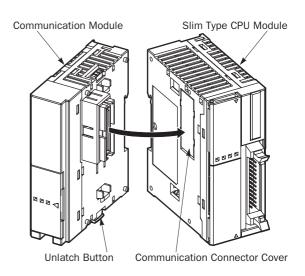

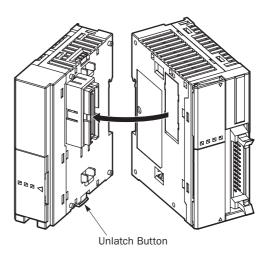

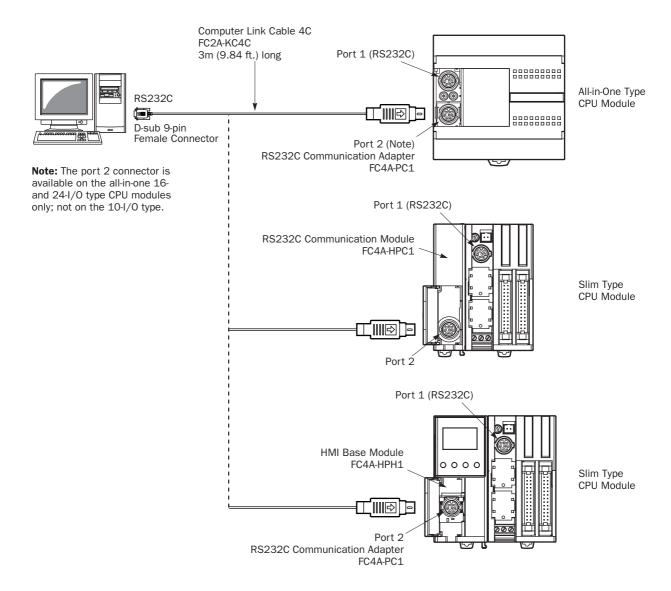

# Communication Adapter (All-in-one 16- and 24-I/O type CPU modules) Communication Module (Slim type CPU modules)

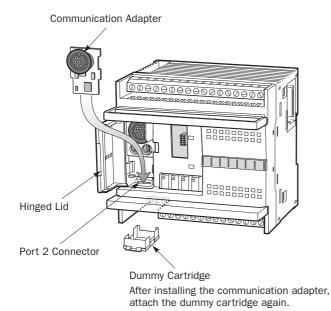

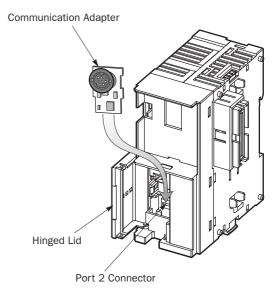

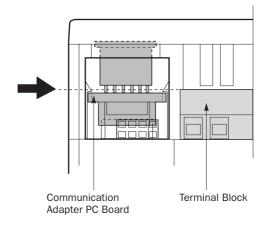

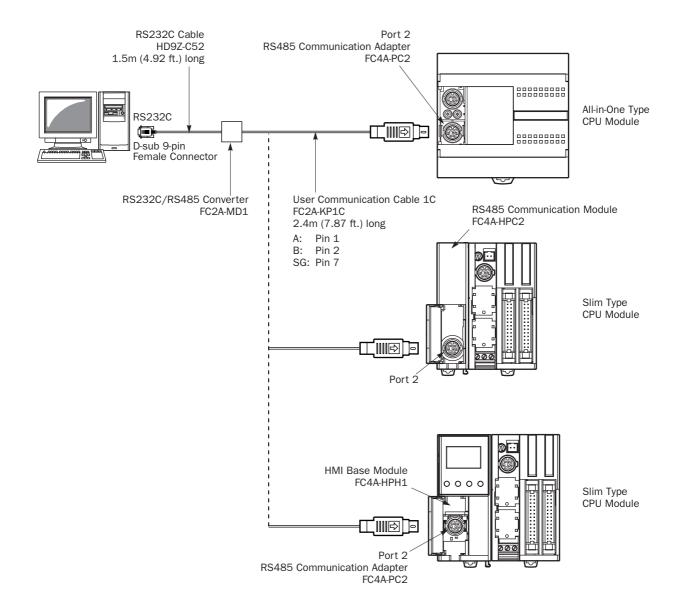

In addition to the standard RS232C port 1, the all-in-one 16- and 24-I/O type CPU modules feature a port 2 connector to install an optional RS232C or RS485 communication adapter. All slim type CPU modules can be used with an optional RS232C or RS485 communication module to add communication port 2. With an optional HMI base module mounted with a slim type CPU module, an optional RS232C or RS485 communication adapter can also be installed on the HMI base module.

| RS232C Communication Adapter<br>RS232C Communication Module | Used for computer link 1:1 communication, user communication, and modem communication.                                                                       |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RS485 Communication Adapter<br>RS485 Communication Module   | Available in mini DIN connector and terminal block styles. Used for computer link 1:1 or 1:N communication, user communication, and data link communication. |

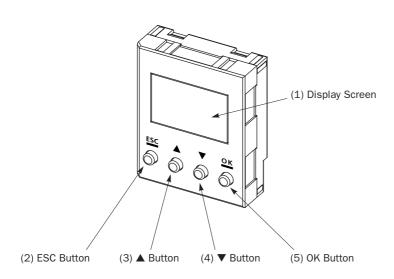

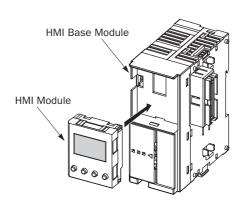

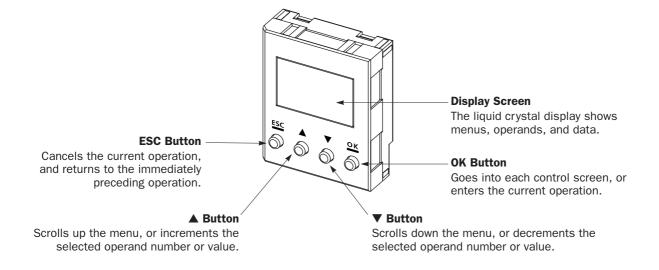

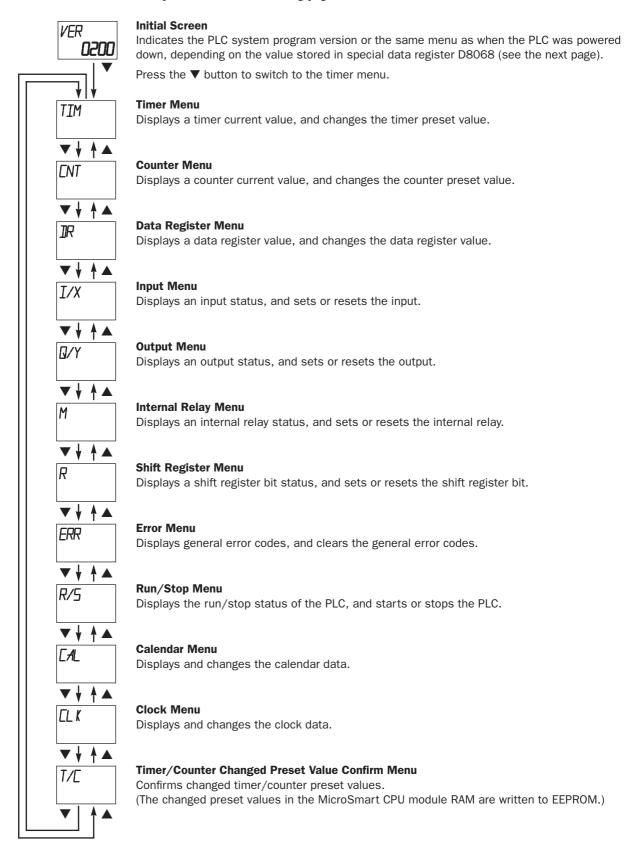

# **HMI Module (all CPU modules)**

An optional HMI module can be installed on any all-in-one type CPU module, and also on the HMI base module mounted next to any slim type CPU module. The HMI module makes it possible to manipulate the RAM data in the CPU module without using the Online menu options in WindLDR.

HMI module functions include:

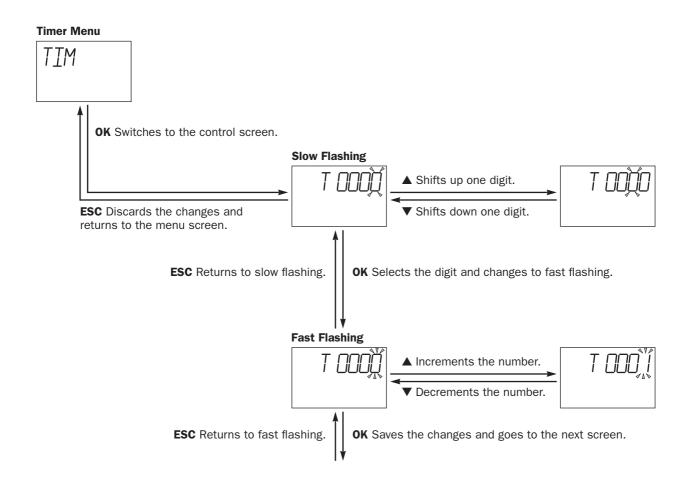

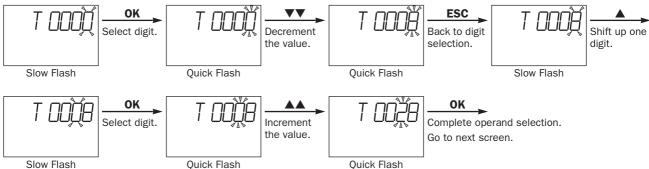

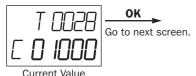

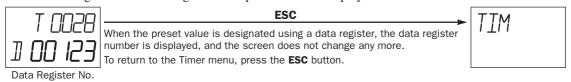

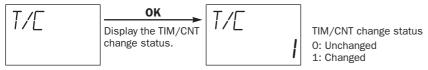

- Displaying timer/counter current values and changing timer/counter preset values

- Displaying and changing data register values

- Setting and resetting bit operand statuses, such as inputs, outputs, internal relays, and shift register bits

- Displaying and clearing error data

- Starting and stopping the PLC

- Displaying and changing calendar/clock data (only when using the clock cartridge)

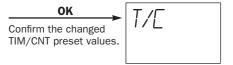

- Confirming changed timer/counter preset values

#### **Clock Cartridge (all CPU modules)**

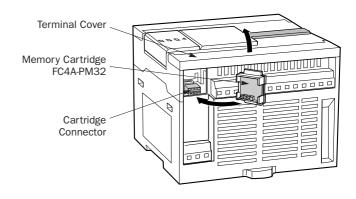

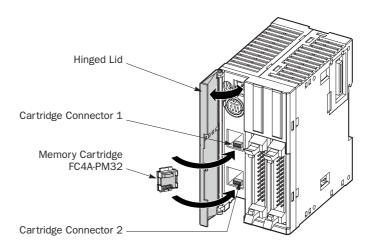

An optional clock cartridge can be installed on the CPU module to store real time calendar/clock data for use with advanced instructions to perform time-scheduled control.

# Memory Cartridge (all CPU modules)

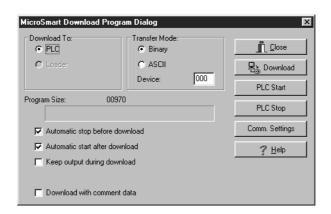

A user program can be stored on an optional memory cartridge using WindLDR. The memory cartridge can be installed on another CPU module to replace user programs without the need for connecting to a computer. The original user program in the CPU module is restored after removing the memory cartridge. The user program on the memory cartridge can also be downloaded to the CPU module. The download option is selected using WindLDR.

## Analog I/O Modules (all CPU modules except the all-in-one 10- and 16-I/O types)

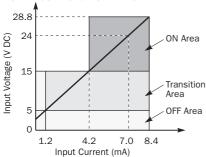

Analog I/O modules are available in 3-I/O types, 2-input type, and 1-output type. The input channel can accept either voltage (0 to 10V DC) and current (4 to 20 mA) signals or thermocouple (types K, J, and T) and resistance thermometer (Pt 100) signals. The output channel generates voltage (0 to 10V DC) and current (4 to 20 mA) signals.

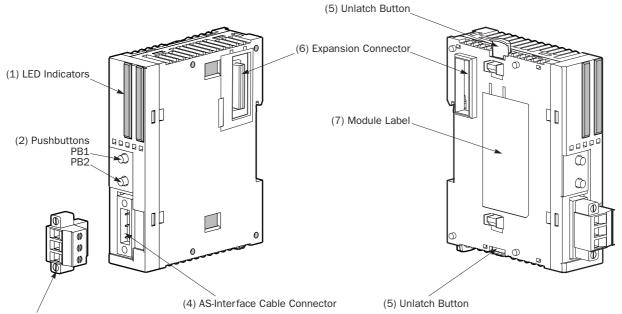

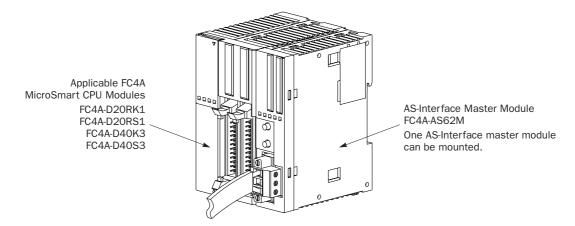

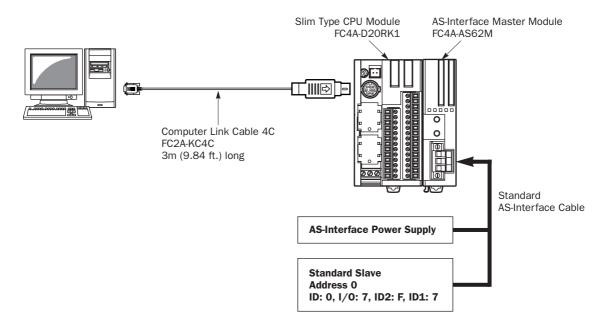

## AS-Interface Master Module (slim type 20-I/O relay output and 40-I/O types)

Four upgraded slim type CPU modules (FC4A-D20RK1, FC4A-D20RS1, FC4A-D40K3, and FC4A-D40S3) with system program ver. 201 and higher can use the AS-Interface master module, and have additional internal relays and data registers to communicate with slaves, such as actuators and sensors, through the AS-Interface bus. For details about AS-Interface module and AS-Interface communication, see page 2-58 and chapter 28.

# **Special Functions**

The MicroSmart features various special functions packed in the small housing as described below. For details about these functions, see the following chapters.

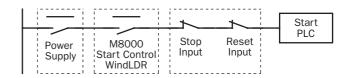

# **Stop and Reset Inputs**

Any input terminal on the CPU module can be designated as a stop or reset input to control the MicroSmart operation.

# RUN/STOP Selection at Startup when "Keep" Data is Broken

When data to be kept such as "keep" designated counter values are broken while the CPU is powered down, the user can select whether the CPU starts to run or not to prevent undesirable operation at the next startup.

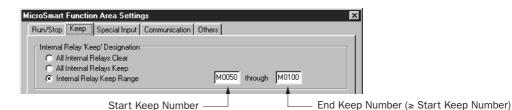

# "Keep" or "Clear" Designation of CPU Data

Internal relays, shift register bits, counter current values, and data register values can be designated to be kept or cleared when the CPU is powered down. All or a specified range of these operands can be designated as keep or clear types.

#### **High-speed Counter**

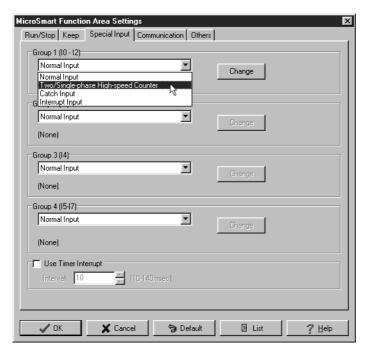

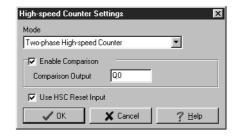

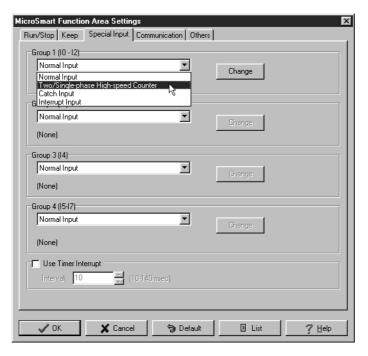

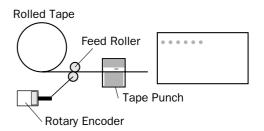

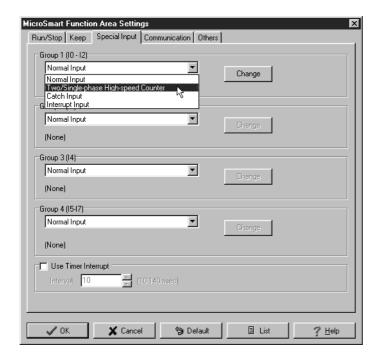

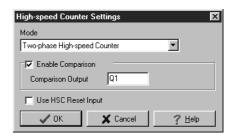

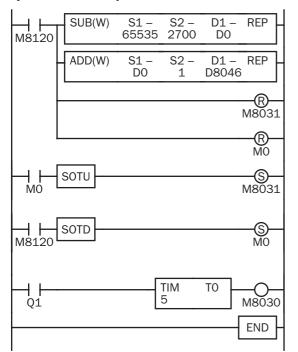

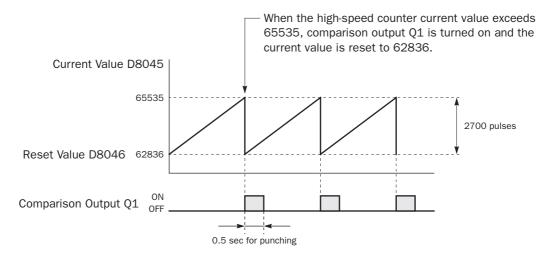

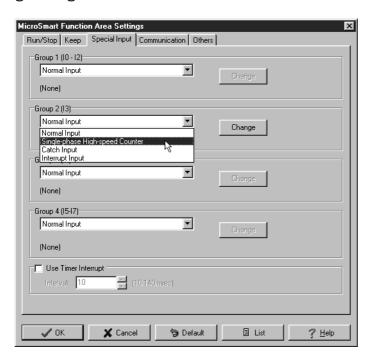

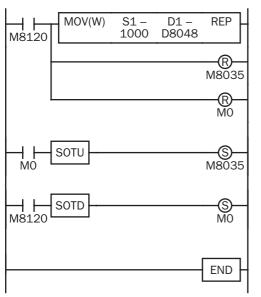

The MicroSmart has four built-in high-speed counters to make it possible to count up to 65,535 (FFFFh) high-speed pulses which cannot be counted by the normal user program processing. One high-speed counter (all-in-one type CPU modules) or two high-speed counters (slim type CPU modules) can be used as either two-phase or single-phase high-speed counters at a maximum count input frequency of 20 kHz. Three or two others are single-phase high-speed counters with a maximum counting frequency of 5 kHz. The high-speed counters can be used for simple positioning control and simple motor control.

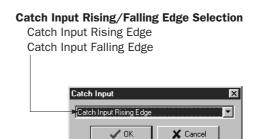

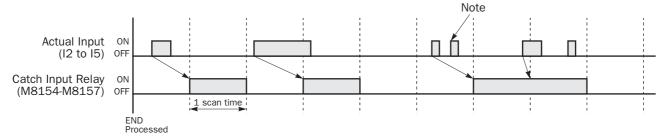

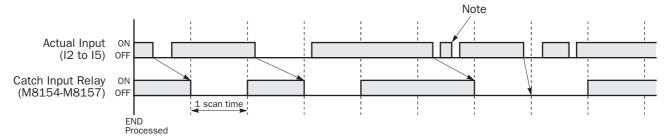

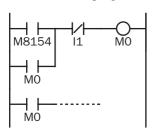

## **Catch Input**

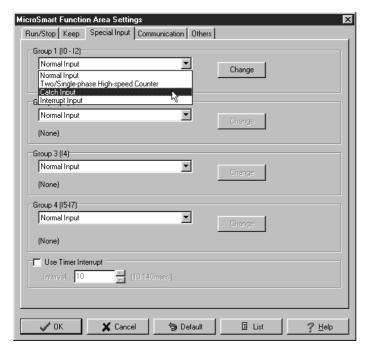

Four inputs can be used as catch inputs. The catch input makes sure to receive short input pulses (rising pulse of  $40 \mu s$  or falling pulse of  $150 \mu s$  minimum) from sensors without regard to the scan time.

## **Interrupt Input**

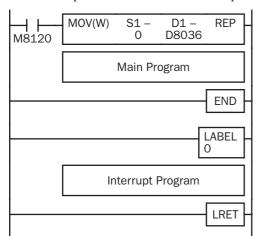

Four inputs can be used as interrupt inputs. When a quick response to an external input is required, such as positioning control, the interrupt input can call a subroutine to execute an interrupt program.

# **Timer Interrupt**

In addition to the interrupt input, slim type CPU modules FC4A-D20RK1, FC4A-D20RS1, FC4A-D40K1, and FC4A-D40S1 have a timer interrupt function. When a repetitive operation is required, the timer interrupt can be used to call a subroutine repeatedly at predetermined intervals of 10 through 140 ms.

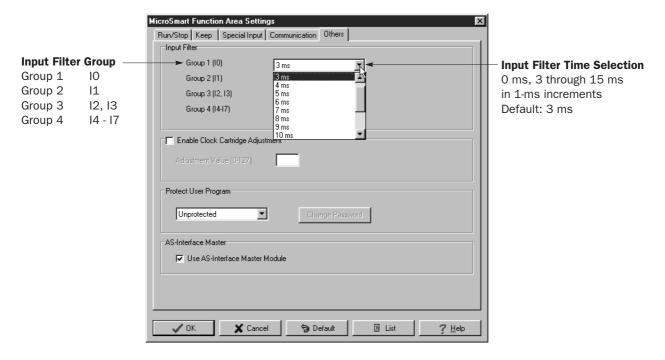

## **Input Filter**

The input filter can be adjusted for eight inputs to reject input noises. Selectable input filter values to pass input signals are 0 ms, and 3 through 15 ms in 1-ms increments. The input filter rejects inputs shorter than the selected input filter value minus 2 ms. This function is useful for eliminating input noises and chatter in limit switches.

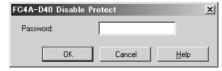

#### **User Program Read/Write Protection**

The user program in the CPU module can be protected against reading and/or writing by including a password in the user program. Read protection without a password is also available to inhibit reading completely.

# **Constant Scan Time**

The scan time may vary whether basic and advanced instructions are executed or not depending on input conditions to these instructions. When performing repetitive control, the scan time can be made constant by entering a required scan time value into a special data register reserved for constant scan time.

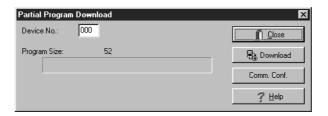

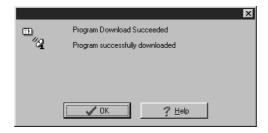

#### **Partial Program Download**

Normally, the CPU module has to be stopped before downloading a user program. All CPU modules (except the all-in-one 10-I/O type) have run-time program download capabilities to download a user program containing small changes while the CPU is running in either 1:1 or 1:N computer link system. This function is particularly useful to make small modifications to the user program and confirm the changes while the CPU is running.

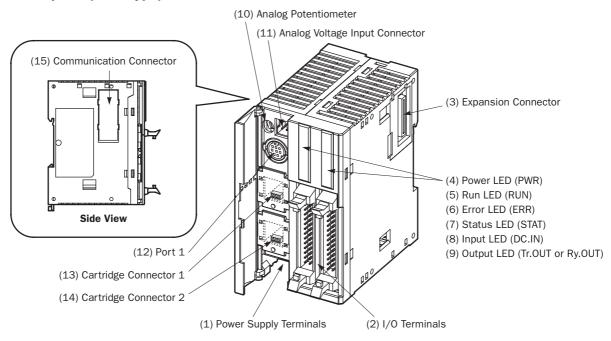

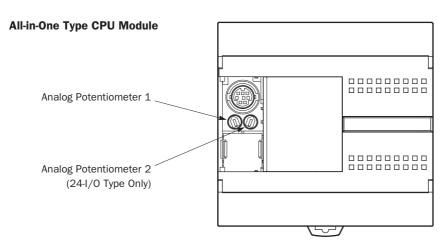

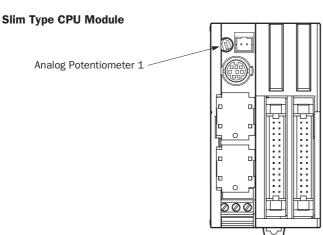

# **Analog Potentiometer**

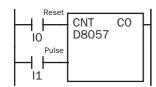

All CPU modules have an analog potentiometer, except the all-in-one 24-I/O type CPU module has two analog potentiometers. The values (0 through 255) set with analog potentiometers 1 and 2 are stored to special data registers. The analog potentiometer can be used to change the preset value for a timer or counter.

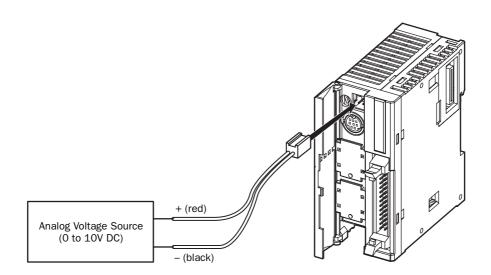

# **Analog Voltage Input**

Every slim type CPU module has an analog voltage input connector. When an analog voltage of 0 through 10V DC is applied to the analog voltage input connector, the signal is converted to a digital value of 0 through 255 and stored to a special data register. The data is updated in every scan.

#### **Pulse Output**

Slim type CPU modules have pulse output instructions to generate high-speed pulse outputs from transistor output terminals used for simple position control applications, illumination control, trapezoidal control, and zero-return control.

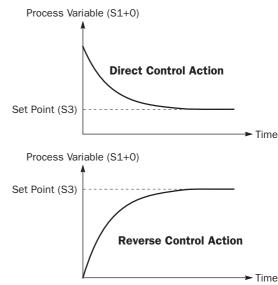

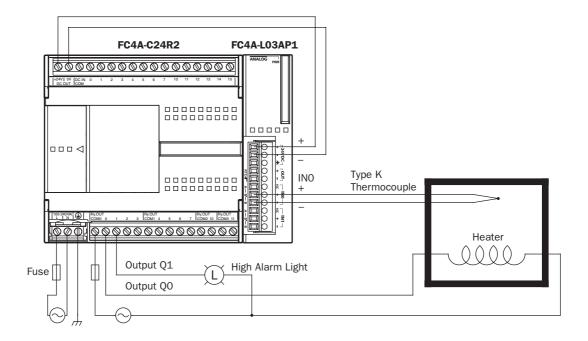

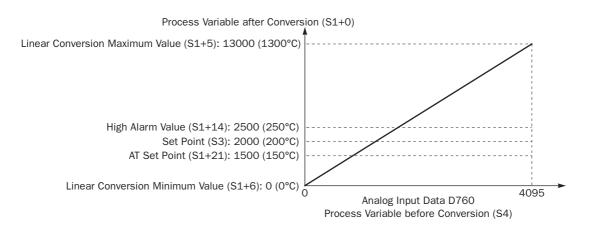

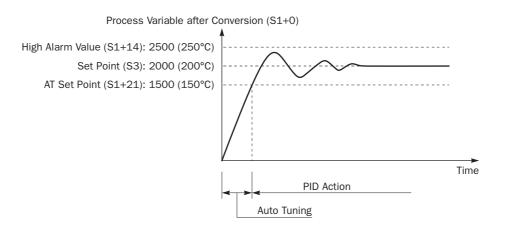

#### PID Control

All CPU modules (except the all-in-one 10- and 16-I/O types) have the PID instruction, which implements a PID (proportional, integral, and derivative) algorithm with built-in auto tuning to determine PID parameters. This instruction is primarily designed for use with an analog I/O module to read analog input data, and turns on and off a designated output to perform PID control in applications such as temperature control. In addition, the PID instruction can also generate an analog output using an analog I/O module.

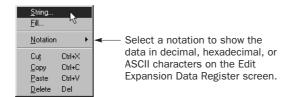

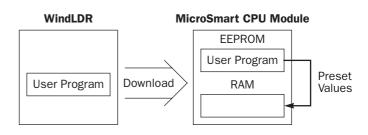

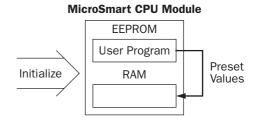

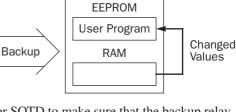

#### **Expansion Data Register**

Slim type CPU modules FC4A-D20RK1, FC4A-D20RS1, FC4A-D40K3, and FC4A-D40S3 have expansion data registers D2000 through D7999. Numerical data can be set to expansion data registers using WindLDR. When downloading the user program, the preset values of the expansion data registers are also downloaded to the EEPROM in the CPU module. Since the data in the EEPROM is non-volatile, the preset values of the expansion data registers are maintained semi-permanently and loaded to the RAM each time the CPU is powered up.

# **System Setup**

This section illustrates system setup configurations for using powerful communication functions of the MicroSmart.

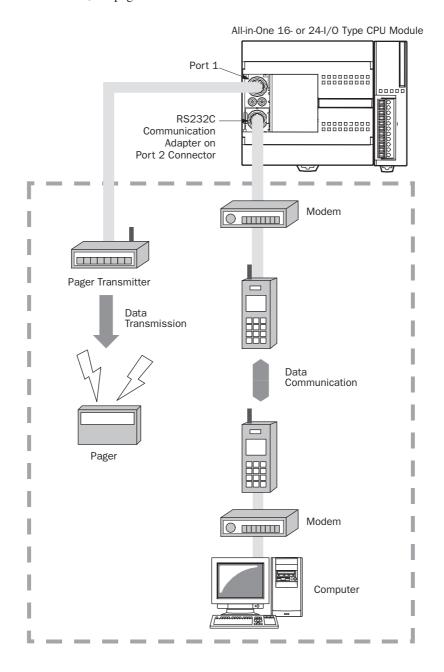

# **User Communication and Modem Communication System**

The all-in-one 16- and 24-I/O type MicroSmart CPU modules have port 1 for RS232C communication and port 2 connector. An optional RS232C or RS485 communication adapter can be installed on the port 2 connector. With an RS232C communication adapter installed on port 2, the 16- or 24-I/O type MicroSmart CPU module can communicate with two RS232C devices at the same time.

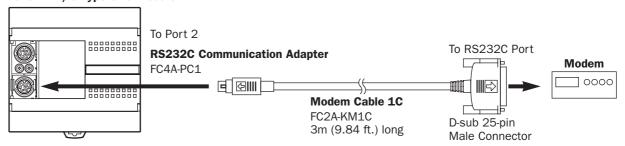

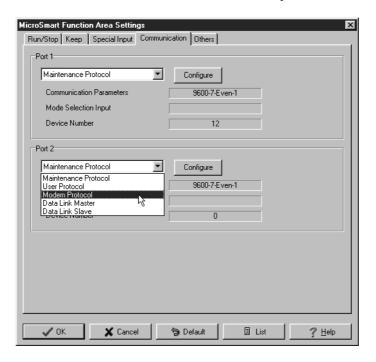

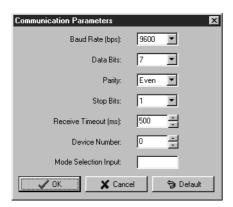

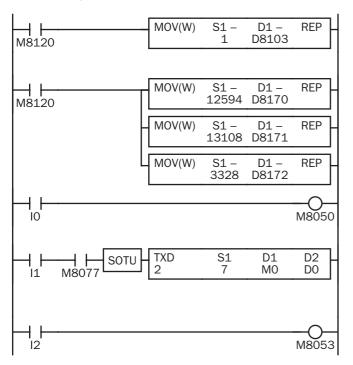

The figure below illustrates a system setup of user communication and modem communication. In this example, the operating status of a remote machine is monitored on a computer through modems connected to port 2 and the data is transferred through port 1 to a pager transmitter using the user communication.

The same system can be set up using any slim type CPU module and an optional RS232C communication module.

For details about the user communication, see page 17-1.

For details about the modem mode, see page 27-1.

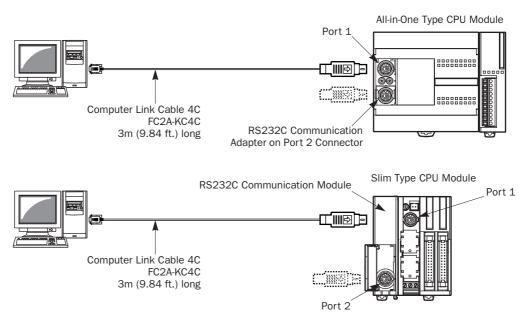

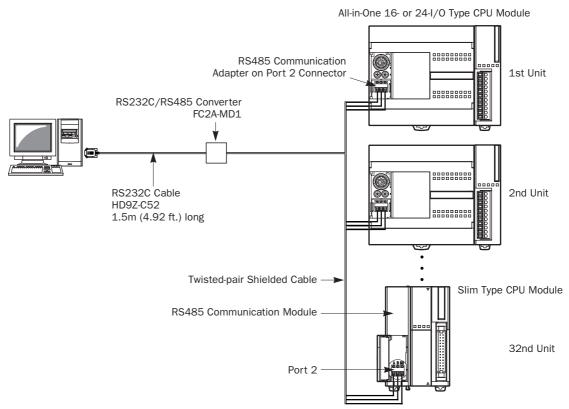

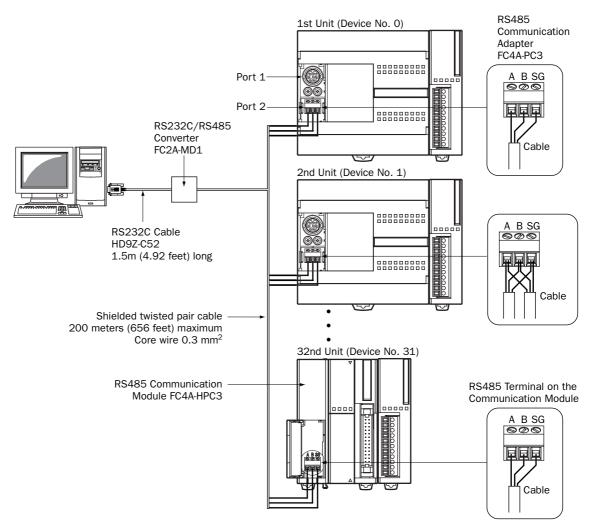

# **Computer Link System**

When the MicroSmart is connected to a computer, operating status and I/O status can be monitored on the computer, data in the CPU module can be monitored or updated, and user programs can be downloaded and uploaded. When an optional RS485 communication adapter is installed on the port 2 connector of the all-in-one 16- or 24-I/O type CPU modules or when an optional RS485 communication module is mounted with any slim type CPU modules, a maximum of 32 CPU modules can be connected to one computer in the 1:N computer link system.

For details about the computer link communication, see pages 4-1 and 26-1.

## **Computer Link 1:1 Communication**

# **Computer Link 1:N Communication**

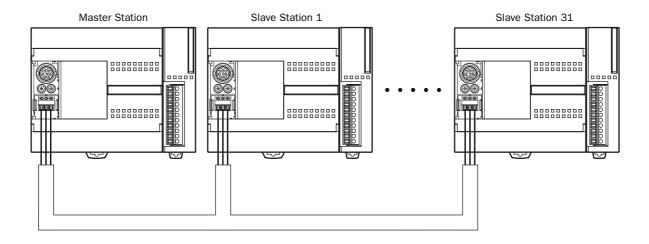

# **Data Link System**

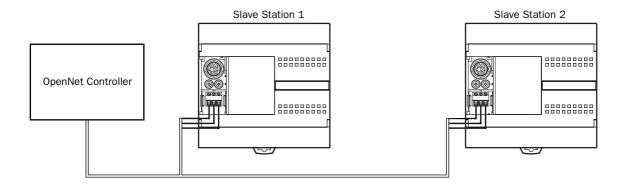

With an optional RS485 communication adapter installed on the port 2 connector, one 16- or 24-I/O type CPU module at the master station can communicate with 31 slave stations through the RS485 line to exchange data and perform distributed control effectively. The RS485 terminals are connected with each other using a 2-core twisted pair cable.

The same data link system can also be set up using any slim type CPU modules mounted with RS485 communication modules.

For details about the data link communication, see page 25-1.

# **Basic System**

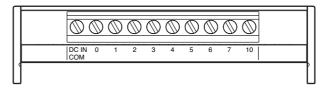

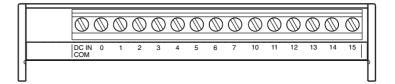

The all-in-one 10-I/O type CPU module has 6 input terminals and 4 output terminals. The 16-I/O type CPU module has 9 input terminals and 7 output terminals. The 24-I/O type CPU module has 14 input terminals and 10 output terminals. Only the 24-I/O type CPU module has an expansion connector to connect I/O modules. When four 16-point input or output modules are connected to the 24-I/O type CPU module, the I/O points can be expanded to a maximum of 88 points.

Any slim type CPU module can add a maximum of seven expansion I/O modules.

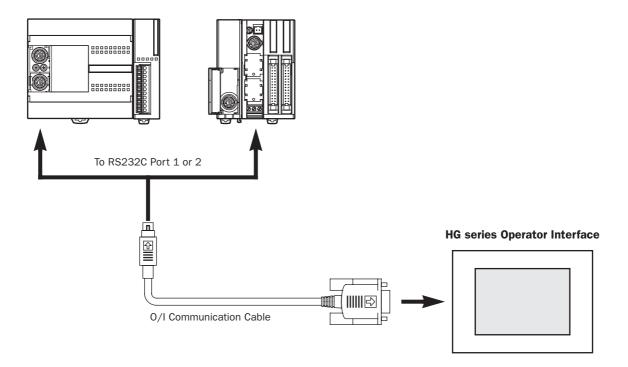

# **Operator Interface Communication System**

The MicroSmart can communicate with IDEC's HG series operator interfaces through RS232C port 1 and port 2.

Optional cables are available for connection between the MicroSmart and HG series operator interfaces. When installing an optional RS232C communication adapter on the all-in-one type CPU module or an optional RS232C communication module on the slim type CPU module, two operator interfaces can be connected to one MicroSmart CPU module.

For details about communication settings, see the user's manual for the operator interface.

# **Applicable Cables to Operator Interfaces**

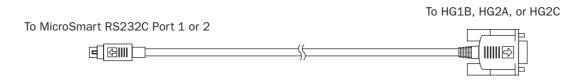

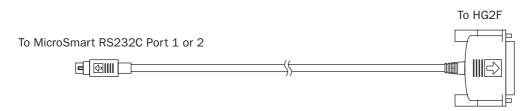

| Operator Interface      | O/I Communication Cable | For Use on MicroSmart    |

|-------------------------|-------------------------|--------------------------|

| HG1B. HG2A Series       | FC4A-KC1C               | RS232C port 1 and port 2 |

| ngib, ngza selles       | HG9Z-XC183              | Port 2 only              |

| HG2F, HG3F, HG4F Series | FC4A-KC2C               | RS232C port 1 and port 2 |

| ngzr, ngsr, ng4r senes  | HG9Z-3C125              | Port 2 only              |

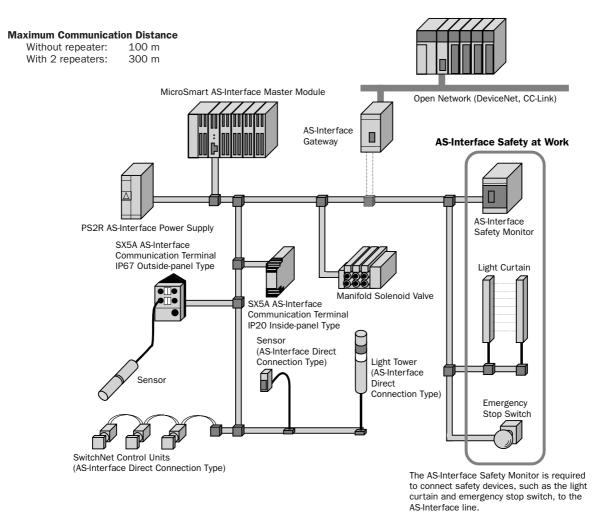

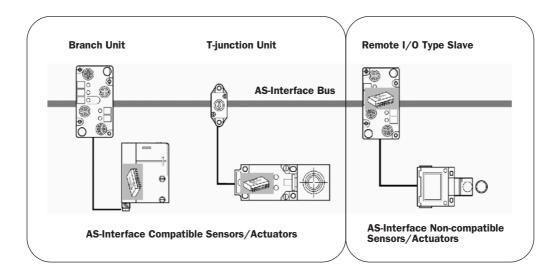

## **AS-Interface Network**

# Actuator-Sensor-Interface, abbreviated AS-Interface

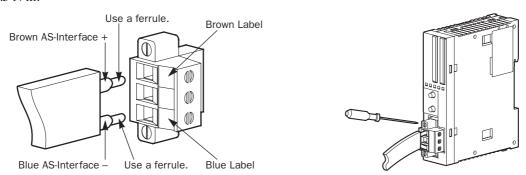

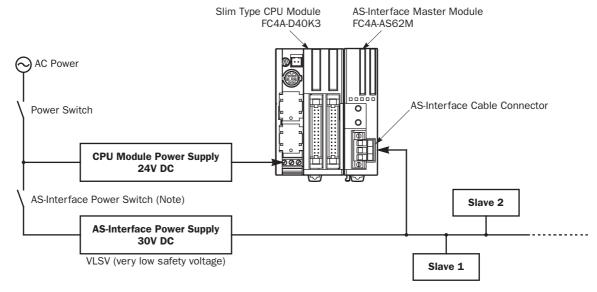

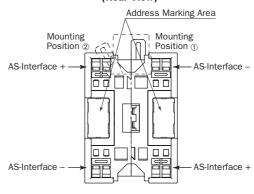

The MicroSmart can be connected to the AS-Interface network using the AS-Interface master module (FC4A-AS62M).

AS-Interface is a type of field bus that is primarily intended to be used to control sensors and actuators. AS-Interface is a network system that is compatible with the IEC62026 standard and is not proprietary to any one manufacturer. A master device can communicate with slave devices such as sensors, actuators, and remote I/Os, using digital and analog signals transmitted over the AS-Interface bus.

The AS-Interface system is comprised of the following three major components:

- One master, such as the MicroSmart AS-Interface master module

- One or more slave devices, such as sensors, actuators, switches, and indicators

- Dedicated 30V DC AS-Interface power supply (26.5 to 31.6V DC)

These components are connected using a two-core cable for both data transmission and AS-Interface power supply. AS-Interface employs a simple yet efficient wiring system and features automatic slave address assignment function, while installation and maintenance are also very easy.

For details about AS-Interface communication, see page 2-58 and chapter 28.

**SwitchNet**<sup>™</sup> SwitchNet is an IDEC trademark for pushbuttons, pilot lights, and other control units capable of direct connection to the AS-Interface. SwitchNet devices are completely compatible with AS-Interface Ver. 2.1.

# 2: Module Specifications

# Introduction

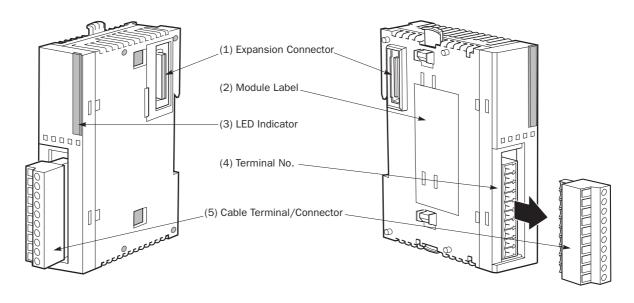

This chapter describes MicroSmart modules, parts names, and specifications of each module.

Available modules include all-in-one type and slim type CPU modules, digital input modules, digital output modules, mixed I/O modules, analog I/O modules, HMI module, HMI base module, communication adapters, communication modules, memory cartridge, and clock cartridge.

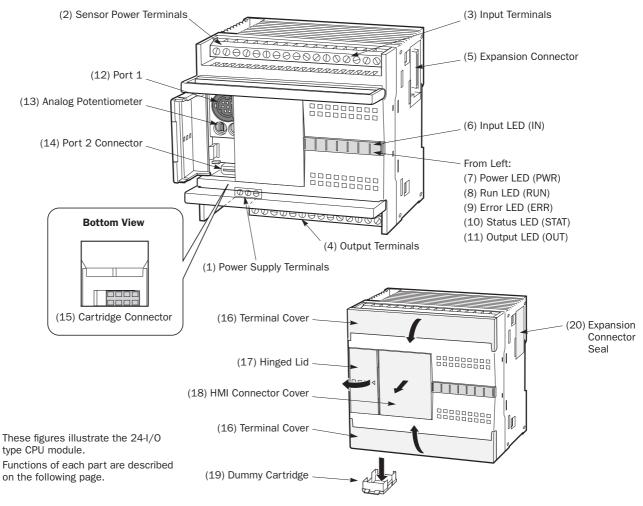

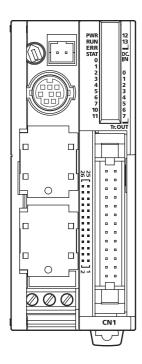

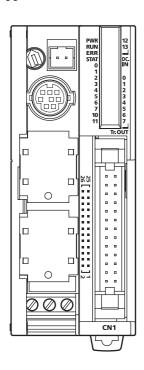

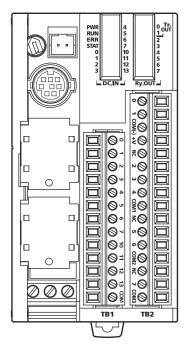

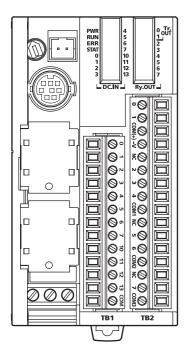

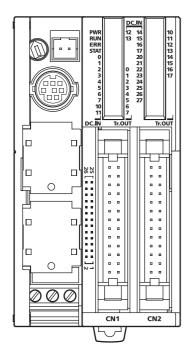

# **CPU Modules (All-in-One Type)**

All-in-one type CPU modules are available in 10-, 16-, and 24-I/O types. The 10-I/O type has 6 input and 4 output terminals, the 16-I/O type 9 input and 7 output terminals, and the 24-I/O type 14 input and 10 output terminals. Every all-in-one type CPU module has communication port 1 for RS232C communication. In addition, the 16- and 24-I/O type CPU modules have port 2 connector to install an optional RS232C or RS485 communication adapter for 1:N computer link, modem communication, or data link communication. Every all-in-one type CPU module has a cartridge connector to install an optional memory cartridge or clock cartridge.

# **CPU Module Type Numbers (All-in-One Type)**

| Power Voltage           | <b>10-I/O Type</b> | <b>16-I/O Type</b> | 24-I/O Type |

|-------------------------|--------------------|--------------------|-------------|

| 100 -240V AC (50/60 Hz) | FC4A-C10R2         | FC4A-C16R2         | FC4A-C24R2  |

| 24V DC                  | FC4A-C10R2C        | FC4A-C16R2C        | FC4A-C24R2C |

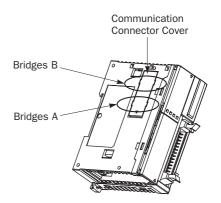

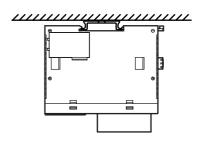

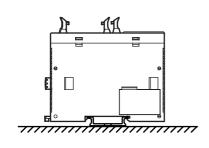

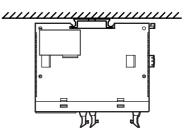

# Parts Description (All-in-One Type)

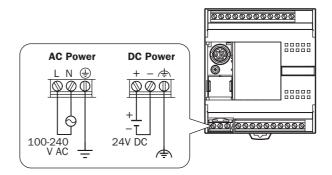

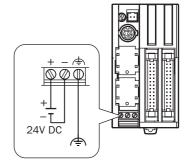

#### (1) Power Supply Terminals

Connect power supply to these terminals. Power voltage 100-240V AC or 24V DC. See page 3-16.

## (2) Sensor Power Terminals (AC power type only)

For supplying power to sensors (24V DC, 250mA). These terminals can be used for supplying power to input circuits. Use the sensor power supply only for supplying power to input devices connected to the MicroSmart.

#### (3) Input Terminals

For connecting input signals from input devices such as sensors, pushbuttons, and limit switches. The input terminals accept both sink and source DC input signals.

## (4) Output Terminals

For connecting output signals to output devices such as electromechanical relays and solenoid valves. The internal output relay is rated at 240V AC/2A or 30V DC/2A.

# (5) Expansion Connector (24-I/O type CPU module only)

For connecting digital and analog I/O modules to the 24-I/O type CPU module.

#### (6) Input LED (IN)

Turns on when a corresponding input is on.

#### (7) Power LED (PWR)

Turns on when power is supplied to the CPU module.

#### (8) Run LED (RUN)

Turns on when the CPU module is executing the user program.

# (9) Error LED (ERR)

Turns on when an error has occurred in the CPU module.

## (10) Status LED (STAT)

The status LED can be turned on or off using the user program to indicate a specified status.

# (11) Output LED (OUT)

Turns on when a corresponding output is on.

## (12) Port 1 (RS232C)

For connecting a computer to download a user program and monitor the PLC operation on a computer using WindLDR.

## (13) Analog Potentiometer

Sets a value of 0 through 255 to a special data register. The 10- and 16-I/O types have one potentiometer. The 24-I/O type has two potentiometers. The analog potentiometer can be used to set a preset value for an analog timer.

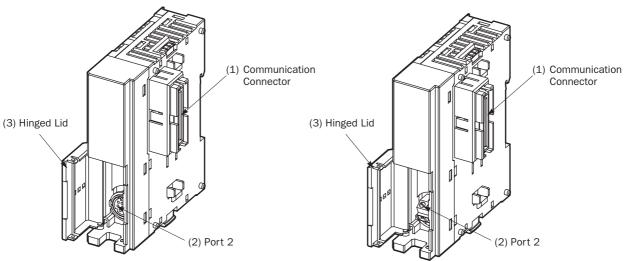

## (14) Port 2 Connector (16- and 24-I/O type CPU modules only)

For connecting an optional RS232C or RS485 communication adapter.

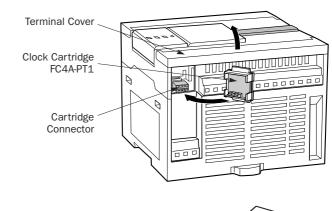

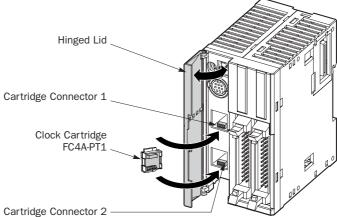

# (15) Cartridge Connector

For connecting an optional memory cartridge or clock cartridge.

# (16) Terminal Cover

For protecting the input and output terminals. When wiring the terminals, open the covers.

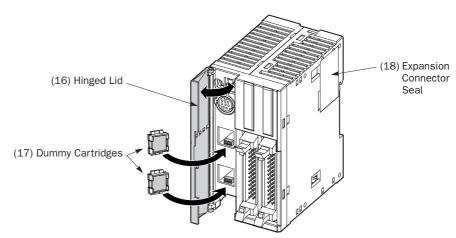

#### (17) Hinged Lid

Open the lid to gain access to the port 1, port 2 connector, and analog potentiometer.

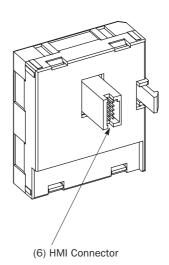

# (18) HMI Connector Cover

Remove the HMI connector cover when using an optional HMI module.

#### (19) Dummy Cartridge

Remove the dummy cartridge when using an optional memory cartridge or clock cartridge.

# (20) Expansion Connector Seal (24-I/O type CPU module only)

Remove the expansion connector seal when connecting a digital or analog I/O module.

# **General Specifications (All-in-One Type CPU Module)**

# **Normal Operating Conditions**

| ODLI Madula    | AC Power Type                                                  | FC4A-C10R2                                                                                                                                                                                  | FC4A-C16R2                                | FC4A-C24R2  |  |  |  |

|----------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------|--|--|--|

| CPU Module     | DC Power Type                                                  | FC4A-C10R2C                                                                                                                                                                                 | FC4A-C16R2C                               | FC4A-C24R2C |  |  |  |

| Operating Tem  | perature                                                       | 0 to 55°C (operating ambier                                                                                                                                                                 | 0 to 55°C (operating ambient temperature) |             |  |  |  |

| Storage Temp   | erature                                                        | -25 to +70°C                                                                                                                                                                                |                                           |             |  |  |  |

| Relative Humi  | dity                                                           | 10 to 95% (non-condensing)                                                                                                                                                                  |                                           |             |  |  |  |

| Pollution Degr | ee                                                             | 2 (IEC 60664-1)                                                                                                                                                                             |                                           |             |  |  |  |

| Degree of Pro  | tection                                                        | IP20 (IEC 60529)                                                                                                                                                                            |                                           |             |  |  |  |

| Corrosion Imm  | nunity                                                         | Atmosphere free from corrosive gases                                                                                                                                                        |                                           |             |  |  |  |

| Altitude       |                                                                | Operation: 0 to 2,000m (0 to 6,565 feet) Transport: 0 to 3,000m (0 to 9,840 feet)                                                                                                           |                                           |             |  |  |  |

| Vibration Resi | stance                                                         | When mounted on a DIN rail or panel surface: 5 to 9 Hz amplitude 3.5 mm, 9 to 150 Hz acceleration 9.8 m/s² (1G) 2 hours per axis on each of three mutually perpendicular axes (IEC 61131-2) |                                           |             |  |  |  |

| Shock Resista  | nnce                                                           | $147 \text{ m/s}^2$ (15G), 11 ms duration, 3 shocks per axis on three mutually perpendic axes (IEC 61131-2)                                                                                 |                                           |             |  |  |  |

| ESD Immunity   | Contact discharge: ±6 kV, Air discharge: ±8 kV (IEC 61000-4-2) |                                                                                                                                                                                             |                                           |             |  |  |  |

| Weight         | AC Power Type                                                  | 230g                                                                                                                                                                                        | 250g                                      | 305g        |  |  |  |

| Meigil         | DC Power Type                                                  | 240g                                                                                                                                                                                        | 260g                                      | 310g        |  |  |  |

# **Power Supply**

| ower Suppry                   |                                                                                                                                                                                      |                                                                                                                                                                                                                                                           |                                              |                                            |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------|--|

| Rated Power V                 | /oltage                                                                                                                                                                              | AC power type: 100 to 240V AC, DC power type: 24V DC                                                                                                                                                                                                      |                                              |                                            |  |

| Allowable Volta               | age Range                                                                                                                                                                            | AC power type: 85 to 264V AC, DC power type: 20.4 to 28.8V DC (including ripple)                                                                                                                                                                          |                                              |                                            |  |

| Rated Power F                 | requency                                                                                                                                                                             | AC power type: 50/60 Hz (47 to 63 Hz)                                                                                                                                                                                                                     |                                              |                                            |  |

| Maximum Inpu                  | it Current                                                                                                                                                                           | 250 mA (85V AC) 300 mA (85V AC) 450 mA (85V AC) 160 mA (24V DC) 360 mA (24V DC)                                                                                                                                                                           |                                              |                                            |  |

| AC Power Type Maximum Power   |                                                                                                                                                                                      | FC4A-C10R2: 30VA (264V AC), 20VA (100V AC) (CPU module*) FC4A-C16R2: 31VA (264V AC), 22VA (100V AC) (CPU module*) FC4A-C24R2: 40VA (264V AC), 33VA (100V AC) (CPU module* + 4 I/O modules) *The CPU module power consumption includes 250mA sensor power. |                                              |                                            |  |

| Consumption                   | DC Power Type                                                                                                                                                                        | FC4A-C10R2C: 3.9W (24V E<br>FC4A-C16R2C: 4.6W (24V E<br>FC4A-C24R2C: 8.7W (24V E                                                                                                                                                                          | ules)                                        |                                            |  |

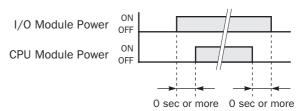

| Allowable Mon<br>Interruption | nentary Power                                                                                                                                                                        | 10 ms (at the rated power voltage)                                                                                                                                                                                                                        |                                              |                                            |  |

| Dielectric Stre               | ngth                                                                                                                                                                                 | Between power and ⊕ or ♠ terminals: 1,500V AC, 1 minute Between I/O and ⊕ or ♠ terminals: 1,500V AC, 1 minute                                                                                                                                             |                                              |                                            |  |

| Insulation Res                | istance                                                                                                                                                                              | Between power and ⊕ or ♠<br>Between I/O and ⊕ or ♠ te                                                                                                                                                                                                     |                                              | ım (500V DC megger)<br>ım (500V DC megger) |  |

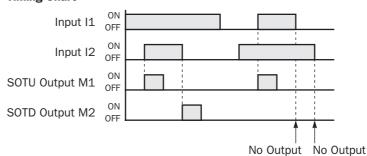

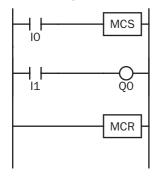

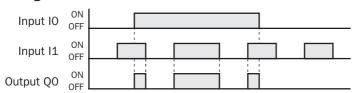

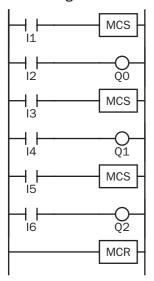

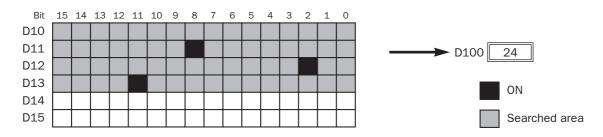

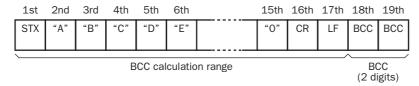

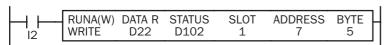

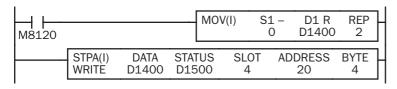

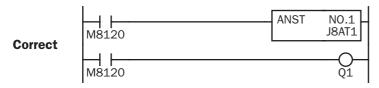

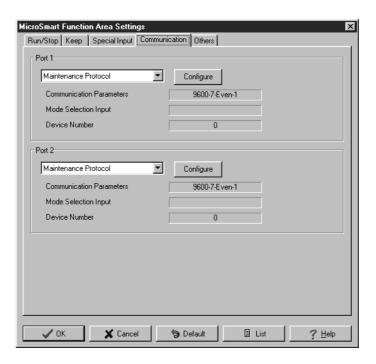

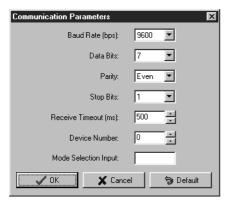

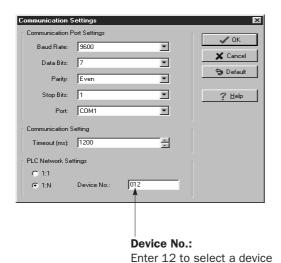

| Noise Resistar                | псе                                                                                                                                                                                  | AC or DC power terminals: I/O terminals (coupling clan                                                                                                                                                                                                    | 1.5 kV, 50 nsec to 1<br>1.5 kV, 50 nsec to 1 | •                                          |  |